# RISC-V Assembly Language and Architecture

*Feb 19th, 2026*

*Alan Johnson*

Draft Xelsys (Alan Johnson) Feb 2026

# Xelsys

*Published by xelsys*

*[www.riscccomputing.com](http://www.riscccomputing.com)*

*[info@alanjohnson.tech](mailto:info@alanjohnson.tech)*

*Copyright © 2026 Alan Johnson. All rights reserved.*

Draft Xelsys (Alan Johnson) Feb 2026

## TARGET AUDIENCE

- Embedded systems enthusiasts

- Computer architecture learners

- Developers interested in system-level programming

- Computer science students

## PRE-REQUISITES

Knowledge of the following areas will ease the journey.

- Familiarity with basic computer hardware

### Microprocessor architecture

- Memory and data buses, register, ALUs, ...

- Experience with Linux ®

- Installation of the Operating System and applications

- Bash

- Basic knowledge of the C programming language

- High school level mathematics<sup>1</sup>

- A RISC-V system<sup>2</sup> or an emulated device.

---

<sup>1</sup> Some of the optional tasks involve linear algebra, which will be more familiar to those at a higher level. A good reference is found at <https://www.khanacademy.org/math/linear-algebra>

<sup>2</sup> RISC-V based hardware is preferred over simulation.

## Summary of the document

### Overview

This book is an in-depth introduction to assembly language programming using the RISC-V instruction set architecture (ISA). It is designed for readers with basic C/Linux experience, embedded systems enthusiasts, computer architecture learners, system-level developers, and computer science students. The text emphasizes foundational concepts, practical coding techniques, and the specifics of the RISC-V unprivileged architecture, with numerous examples, exercises, and diagrams. There may be areas that require supplemental knowledge. The focus is on the RISC-V instruction set - unprivileged architecture.

---

### Structure and Key Topics

- **Assembly vs. High-Level Languages:** Explains the low-level control and transparency of assembly compared to the abstraction of high-level languages.

- **Assembling, Compiling, and Linking:** Describes the process of converting human-readable code to machine code and linking object files.

- **Hardware, Software, Firmware:** Differentiates these core system components.

- **Number Systems:** Covers binary, hexadecimal, BCD, conversions, complements, and arithmetic.

- **Logic Operations:** Introduces AND, OR, XOR, NOT, and truth tables.

- **RISC-V Origins & Architecture:** Discusses the open-source nature, 32/64-bit modes, and instruction extensions (M, F, D, C).

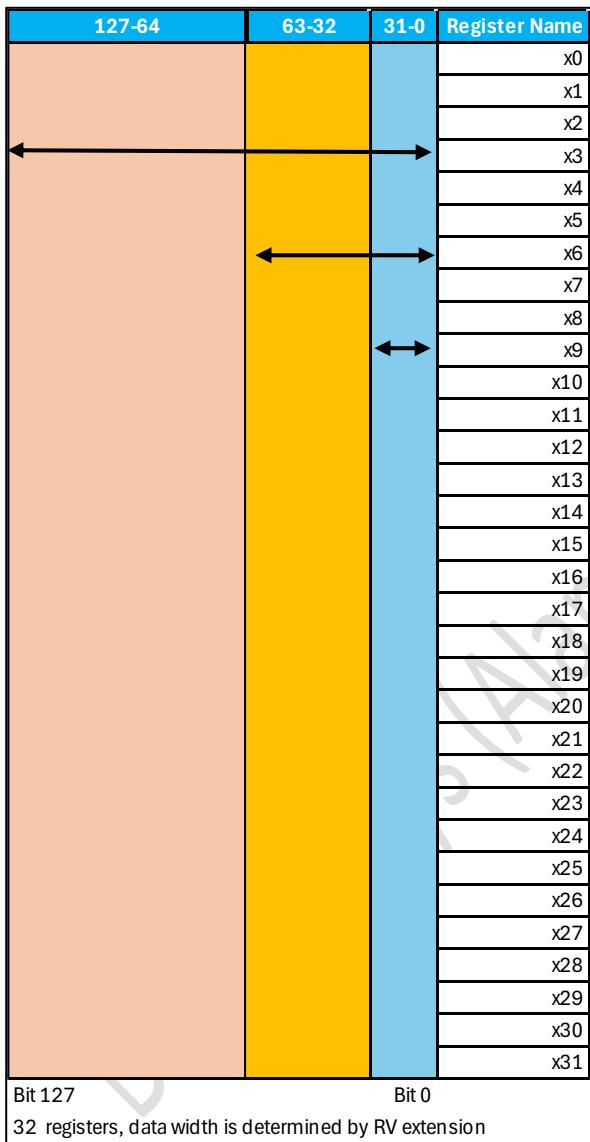

- **Register Set:** Details the 32 general-purpose registers and their ABI names<sup>2</sup>. Programming Concepts

- **Memory Access:** Load/store instructions and addressing modes.

- **Arithmetic/Logic:** Integer math, shifts, multiplication, division, and condition codes.

- **Branching & Loops:** Conditional and unconditional branching, loop counters.

- **Stack, Macros, Functions:** Stack usage, modular code, macro definitions.

- **C and Assembly Integration:** In-line assembly, calling conventions.

- **Floating-Point Arithmetic:** IEEE 754 formats, rounding, comparisons.

- **Vector Operations:** SIMD-style instructions, vector registers, masking, merging.

- **Cross-Compiling and Simulation:** Installation and use of the Spike simulator, toolchain setup, debugging, and cross-compilation for RISC-V on non-native hosts.

---

### Detailed Chapter Highlights

- **Chapter 1:** Lays the groundwork for assembly language, number systems, logic, and the rationale for using assembly.

- **Chapter 2:** Introduces RISC-V architecture, instruction set variants, register conventions, and essential tools (GNU assembler, linker, GDB, objdump, make).

- **Chapter 3:** Focuses on memory operations, addressing modes, linker relaxation, and practical examples of load/store instructions.

- **Chapter 4:** Explores arithmetic and logical operations, including overflow detection, multiplication/division, and shift instructions.

- **Chapter 5:** Covers control flow, loops, conditional and unconditional branching, and program structure.

- **Chapter 6:** Discusses stack management, modular code, macros, and function conventions.

- **Chapter 7:** Explains how to interface assembly with C, use inline assembly, and optimize code.

- **Chapter 8:** Details floating-point operations, IEEE 754 compliance, rounding modes, and exception handling.

- **Chapter 9:** Introduces vector processing, vector registers, SIMD operations, and advanced vector instructions.

- **Chapter 10:** Guides on cross-compiling, using the Spike simulator, and running/debugging RISC-V programs on various platforms

---

### *Appendices and Resources*

- **Appendices:** Include GDB commands, ASCII code tables, references, and assembly directives.

- **Figures, Listings, and Tables:** The book is rich with diagrams, code listings, and tables to illustrate concepts and provide practical reference.

---

### *Notable Features*

- **Practical Examples:** Each chapter includes code samples, exercises, and step-by-step walkthroughs.

- **Toolchain Guidance:** Detailed instructions for setting up and using the GNU toolchain, simulators (CPULator, RARS), and debugging tools.

- **Modern RISC-V Focus:** Emphasizes open-source, extensible, and modern aspects of RISC-V, including vector and floating-point extensions.

- **Integration with C:** Shows how to combine assembly with high-level languages for system-level programming.

## *Conclusion*

This document is a comprehensive, hands-on guide to RISC-V assembly language and architecture, suitable for learners and practitioners aiming to master low-level programming, system architecture, and the RISC-V ecosystem. It balances foundational theory with practical application, making it a valuable resource for both study and reference.

---

Draft Xelsys (Alan Johnson) Feb 2026

## Contents

|                                                                                           |      |

|-------------------------------------------------------------------------------------------|------|

| Chapter 1. The fundamentals of assembly language.....                                     | 1-1  |

| 1.1. What is assembly language?.....                                                      | 1-1  |

| 1.1.1. High-level languages Vs Assembly language.....                                     | 1-1  |

| 1.1.2. Architecture and Machine code.....                                                 | 1-1  |

| 1.1.3. Assembling, compiling and linking.....                                             | 1-2  |

| 1.1.4. Pseudocode .....                                                                   | 1-2  |

| 1.1.5. Why use assembly? .....                                                            | 1-2  |

| 1.2. Hardware Vs Software Vs Firmware .....                                               | 1-3  |

| 1.2.1. Hardware.....                                                                      | 1-3  |

| 1.2.2. Software .....                                                                     | 1-3  |

| 1.3. Number Systems.....                                                                  | 1-3  |

| 1.3.1. <i>Binary, Octal, Hexadecimal</i> .....                                            | 1-3  |

| 1.3.2. Converting Binary to Decimal.....                                                  | 1-5  |

| 1.3.3. Converting Hexadecimal to Decimal .....                                            | 1-9  |

| 1.3.4. <i>Converting Decimal to Hexadecimal</i> .....                                     | 1-10 |

| 1.3.5. Binary Fractions.....                                                              | 1-10 |

| 1.3.6. <i>Converting a binary fraction to decimal</i> .....                               | 1-10 |

| 1.3.7. <i>One and Two's complement</i> .....                                              | 1-11 |

| 1.3.8. <i>Addition and subtraction of binary numbers</i> .....                            | 1-13 |

| 1.3.9. <i>Binary subtraction</i> .....                                                    | 1-14 |

| 1.3.10. <i>Binary multiplication</i> .....                                                | 1-15 |

| 1.3.11. <i>Binary Division</i> .....                                                      | 1-16 |

| 1.3.12. <i>Shift/ Rotate instructions to perform multiply and divide operations</i> ..... | 1-17 |

| 1.3.13. <i>Binary Coded Decimal (BCD)</i> .....                                           | 1-17 |

| 1.3.14. <i>Floating Point</i> .....                                                       | 1-21 |

| 1.4. <i>Logic operations – and, OR, Exclusive OR, NOT</i> .....                           | 1-25 |

| Summary .....                                                                             | 1-28 |

| Exercises for chapter1.....                                                               | 1-29 |

| Chapter 2. Getting Started.....                                                           | 2-1  |

|                   |                                               |      |

|-------------------|-----------------------------------------------|------|

| 2.1.              | Origin of RISC-V.....                         | 2-1  |

| 2.2.              | Architecture .....                            | 2-1  |

| 2.2.1.            | RISC-V Registers .....                        | 2-3  |

| 2.2.2.            | Additional fields funct3 and funct7.....      | 2-12 |

| 2.3.              | Coding Tools .....                            | 2-13 |

| 2.3.1.            | Editing files .....                           | 2-14 |

| 2.3.2.            | Comments .....                                | 2-17 |

| 2.3.3.            | Assembling .....                              | 2-17 |

| 2.3.4.            | Linker.....                                   | 2-18 |

| 2.3.5.            | GDB – The GNU Debugger.....                   | 2-21 |

| 2.3.6.            | Objdump.....                                  | 2-23 |

| 2.3.7.            | <i>Make</i> .....                             | 2-24 |

| 2.4.              | Choosing a candidate platform .....           | 2-25 |

| 2.4.1.            | Hardware Platforms .....                      | 2-25 |

| 2.4.2.            | Emulation and Simulation.....                 | 2-26 |

| 2.4.3.            | Using strace .....                            | 2-37 |

|                   | RISC-V Instructions Covered in Chapter 2..... | 2-38 |

|                   | Exercises for chapter 2.....                  | 2-39 |

| <i>Chapter 3.</i> | <i>Dealing with memory</i> .....              | 3-2  |

| 3.1.              | Load and Store instructions.....              | 3-2  |

| 3.1.1.            | LOAD Instructions (Memory → Registers) .....  | 3-2  |

| 3.2.              | Outputting (Writing) ASCII text .....         | 3-6  |

| 3.3.              | Inputting (reading) values.....               | 3-7  |

| 3.4.              | Relative and absolute addressing.....         | 3-8  |

| 3.4.1.            | RISC-V Assembler Modifiers.....               | 3-9  |

| 3.5.              | Linker Relaxation .....                       | 3-12 |

| 3.5.1.            | Further relaxation example.....               | 3-17 |

| 3.5.2.            | Enhancements to GDB .....                     | 3-20 |

|                   | Exercises for chapter3.....                   | 3-22 |

|                   | RISC-V instructions covered in chapter 3..... | 3-23 |

|                                                                                    |      |

|------------------------------------------------------------------------------------|------|

| Chapter 4. Arithmetic operations (First Pass) .....                                | 4-1  |

| 4.1. Data Sizes.....                                                               | 4-1  |

| 4.2. Integer Instructions .....                                                    | 4-1  |

| 4.2.1. Register ADD .....                                                          | 4-1  |

| 4.2.2. ADD Immediate .....                                                         | 4-7  |

| 4.2.3. MV instruction.....                                                         | 4-11 |

| 4.3. Condition Codes.....                                                          | 4-12 |

| 4.3.1. Detecting an oVerflow condition .....                                       | 4-13 |

| 4.3.2. RVM Instructions.....                                                       | 4-13 |

| 4.3.3. Multiply Instructions .....                                                 | 4-13 |

| 4.3.4. Illustrating the mechanics of 64-bit multiplication going to 128 bits ..... | 4-17 |

| 4.3.5. Divide Instructions.....                                                    | 4-19 |

| 4.3.5.1. Division by zero .....                                                    | 4-19 |

| 4.4. Shift Operations.....                                                         | 4-20 |

| 4.5. Logical Instructions .....                                                    | 4-23 |

| 4.5.1. Logical function observations .....                                         | 4-25 |

| Exercises for chapter 4 .....                                                      | 4-27 |

| RISC-V instructions covered in chapter 4.....                                      | 4-28 |

| Chapter 5. Loops, Branches and Conditions .....                                    | 5-1  |

| 5.1. J-Type and B-Type instructions.....                                           | 5-1  |

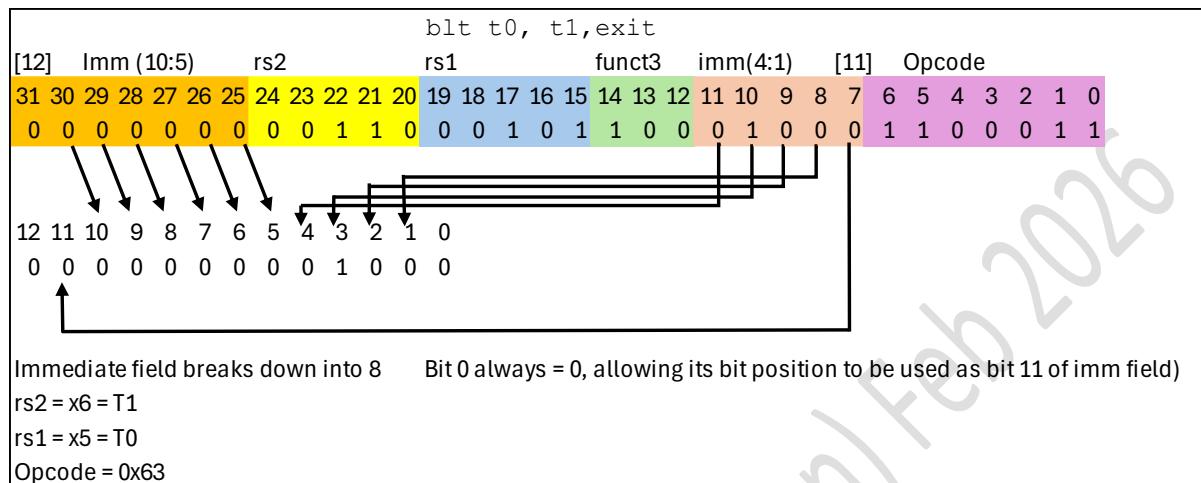

| 5.1.1. B-Type instruction details .....                                            | 5-1  |

| 5.1.2. J-Type instruction details .....                                            | 5-2  |

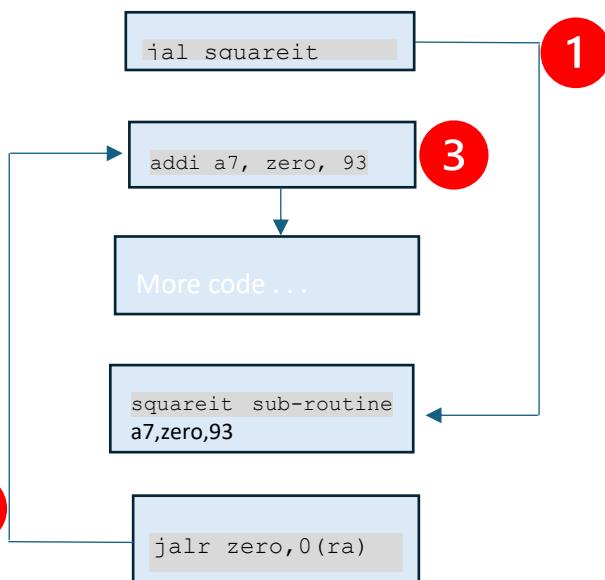

| 5.2. Implementing a loop counter to square numbers .....                           | 5-3  |

| 5.2.1. Summary of jump instructions.....                                           | 5-5  |

| Exercises for chapter 5 .....                                                      | 5-7  |

| RISC-V jump and branch instructions covered in chapter 5 .....                     | 5-8  |

| Chapter 6. The Stack, Macros and Functions.....                                    | 6-1  |

| 6.1. Overview.....                                                                 | 6-1  |

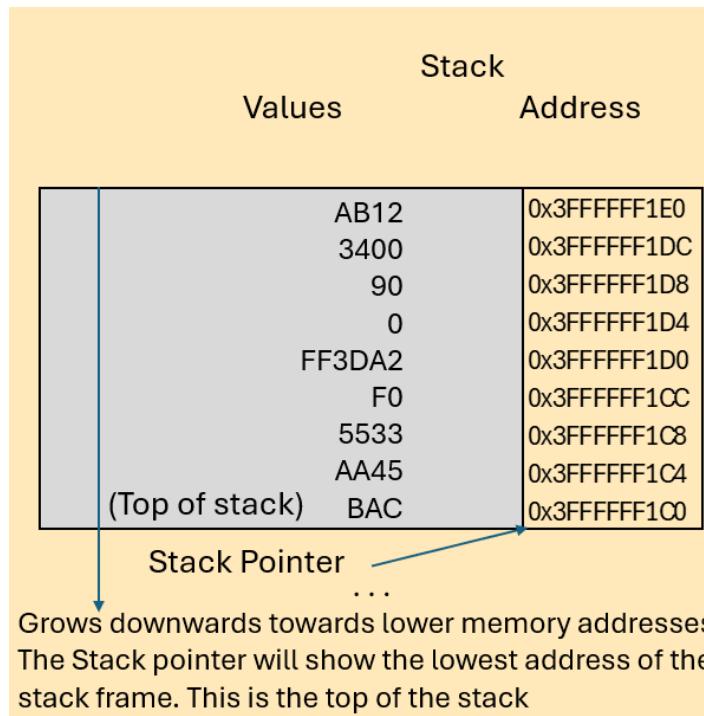

| 6.1.1. The Stack .....                                                             | 6-1  |

| 6.1.2. Functions .....                                                             | 6-3  |

|                                                                 |      |

|-----------------------------------------------------------------|------|

| 6.2. Calling nested routines .....                              | 6-4  |

| 6.2.1. Combining separate programs.....                         | 6-6  |

| 6.3. Macros .....                                               | 6-13 |

| 6.3.1. Using the Stack – further examples .....                 | 6-17 |

| 6.3.2. Macros and routines – numeric labels.....                | 6-28 |

| 6.3.3. Push and Pop Macros.....                                 | 6-30 |

| 6.3.4. Macros and routines – POP and PUSH Caveats .....         | 6-33 |

| Exercises for chapter6.....                                     | 6-34 |

| Summary of instructions used in chapter 6 .....                 | 6-36 |

| Chapter 7. RISC_V assembly and C together .....                 | 7-2  |

| 7.1. Example C code.....                                        | 7-2  |

| 7.1. Optimizing code with GCC.....                              | 7-5  |

| 7.2. C optimization techniques.....                             | 7-5  |

| 7.2.1. Compile-time optimization .....                          | 7-6  |

| 7.2.2. Run-time optimization .....                              | 7-8  |

| 7.3. Calling assembly functions from a high-level language..... | 7-9  |

| 7.3.1. Basic ASM .....                                          | 7-15 |

| 7.3.1. Extended ASM .....                                       | 7-15 |

| 7.4. Format Specifiers.....                                     | 7-19 |

| Exercises for chapter 7 .....                                   | 7-23 |

| Summary of RISC-V instruction used in chapter 7 .....           | 7-24 |

| Chapter 8. Floating-Point .....                                 | 8-1  |

| 8.1. RISC-V floating-point capability .....                     | 8-1  |

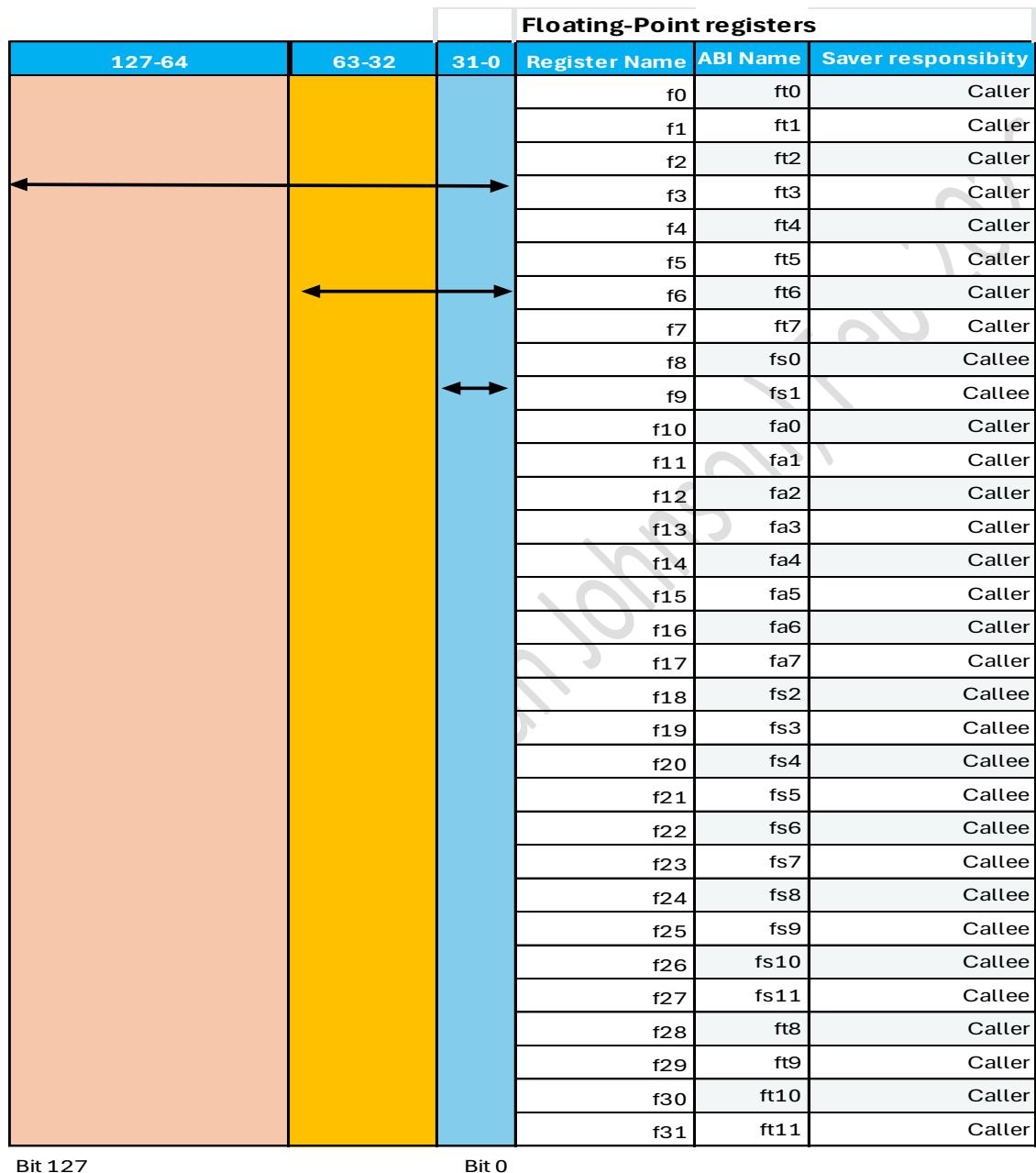

| 8.1.1. Floating-point register set .....                        | 8-1  |

| 8.2. Instruction types.....                                     | 8-3  |

| 8.2.1. Arithmetic instructions.....                             | 8-3  |

| 8.2.2. Load and store instructions.....                         | 8-4  |

| 8.2.3. Convert instructions .....                               | 8-4  |

| 8.2.4. Categorization instructions .....                        | 8-4  |

| 8.2.5. Comparison instructions .....                            | 8-4  |

|                                                                |      |

|----------------------------------------------------------------|------|

| 8.2.6. Miscellaneous instructions.....                         | 8-4  |

| 8.3. Instruction format .....                                  | 8-4  |

| 8.3.1. Floating point control and status register.....         | 8-5  |

| 8.3.2. Rounding Modes .....                                    | 8-6  |

| 8.3.3. Accrued Exception bits.....                             | 8-6  |

| 8.4. Floating-Point comparison instructions .....              | 8-16 |

| 8.5. Floating-point classification instructions.....           | 8-17 |

| 8.6. Exercises for chapter 8 .....                             | 8-21 |

| 8.7. Summary of RISC-V instructions used in chapter 8 .....    | 8-21 |

| Chapter 9. Vector operations.....                              | 9-1  |

| 9.1. Vector system support .....                               | 9-1  |

| 9.2. Vector registers overview.....                            | 9-2  |

| 9.2.1. General purpose vector registers.....                   | 9-2  |

| 9.2.2. Vector CSR's .....                                      | 9-2  |

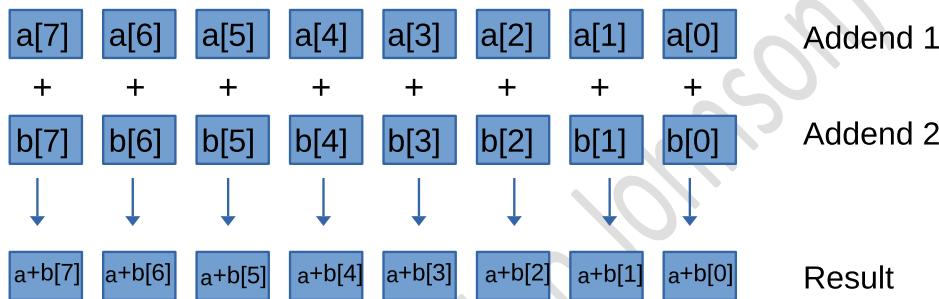

| 9.3. Vector addition/ subtraction example .....                | 9-6  |

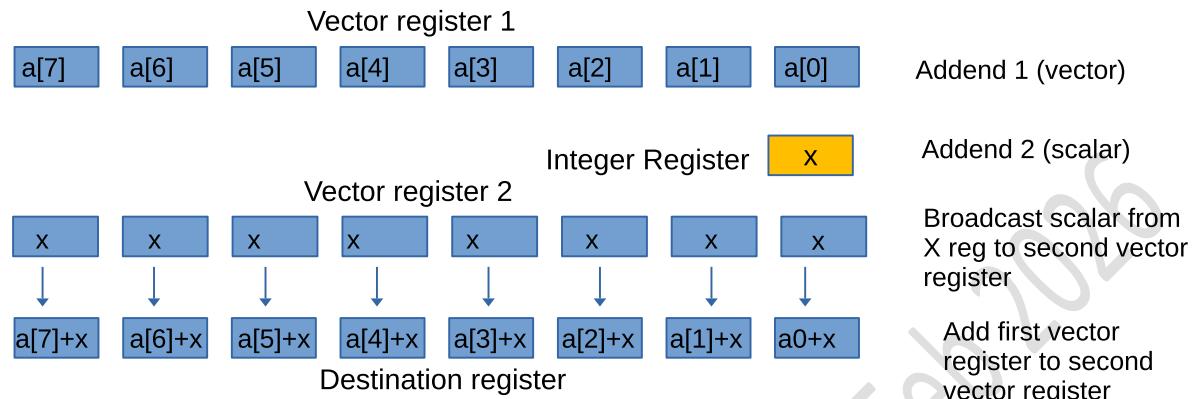

| 9.3.1. Adding a vector and a scalar .....                      | 9-9  |

| 9.3.2. Vector CSR content after execution of Listing 9-2 ..... | 9-12 |

| 9.4. Moving elements with vslide.....                          | 9-12 |

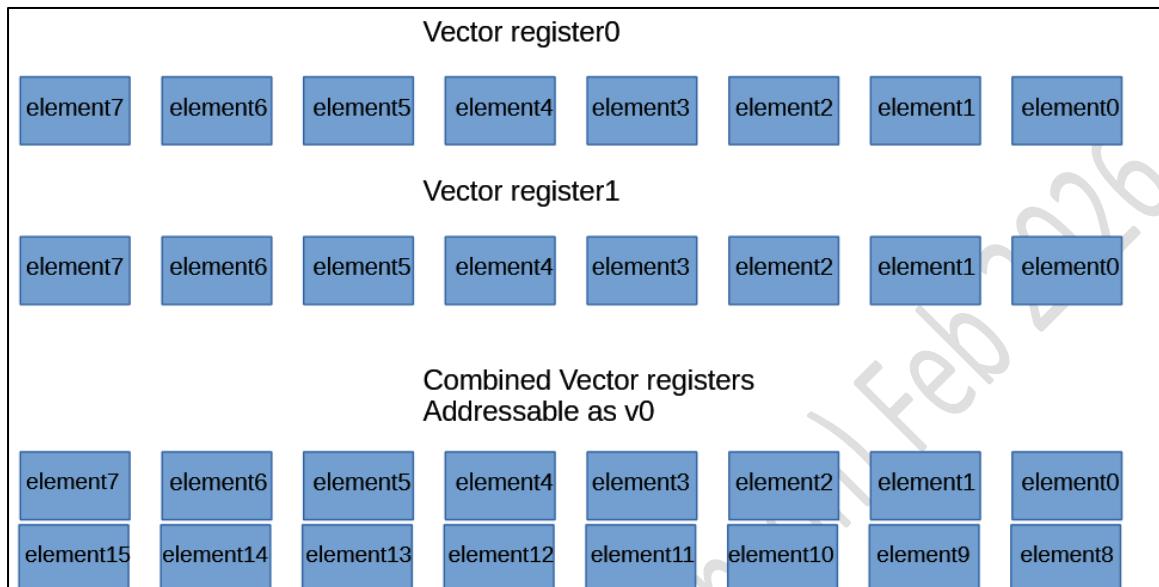

| 9.5. Grouping vector registers.....                            | 9-14 |

| 9.5.1. Masking and merging .....                               | 9-18 |

| Summary of RISC-V instructions used in chapter 9 .....         | 9-22 |

| Chapter 10. Spike simulator and Cross compiling .....          | 10-1 |

| 10.1. Building the Toolchain and Spike .....                   | 10-1 |

| 10.1.1. Installing the toolchain .....                         | 10-3 |

| 10.1.2. Installing Spike and PK .....                          | 10-4 |

| 10.1.3. Spike installation.....                                | 10-4 |

| 10.1.4. PK installation .....                                  | 10-4 |

| 10.1.5. Testing.....                                           | 10-4 |

| 10.2. Cross-compiling C code.....                              | 10-4 |

| 10.3. Cross-assembling and linking.....                        | 10-6 |

|                                             |      |

|---------------------------------------------|------|

| 10.3.1. Using objdump.....                  | 10-6 |

| Further resources.....                      | 10-9 |

| Appendix A. GDB Commonly Used Commands..... | 1    |

| Appendix B. ASCII Code .....                | 1    |

| Appendix C. References and Resources .....  | 1    |

| Appendix D. Assembly Directives .....       | 10-i |

## Figures

|                                                                                               |      |

|-----------------------------------------------------------------------------------------------|------|

| Figure 1-1 Converting Decimal to binary using repeated division by $2_{10}$ .....             | 1-9  |

| Figure 1-2 Converting Decimal to binary using repeated division by $16_{10}$ .....            | 1-10 |

| Figure 1-3 Using shift operations to multiply and divide by two.....                          | 1-17 |

| Figure 1-4 Interpretation of Bias with floating point.....                                    | 1-23 |

| Figure 1-5 Addition of two floating point numbers .....                                       | 1-25 |

| Figure 2-1 RISC-V register layout .....                                                       | 2-4  |

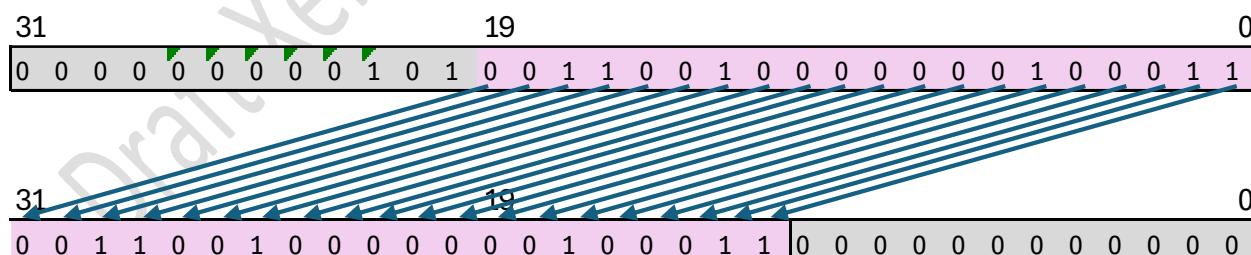

| Figure 2-2 LUI left shift of IMM bits into bits 31:12.....                                    | 2-8  |

| Figure 2-3 Tracing AUIPC and LUI instructions .....                                           | 2-9  |

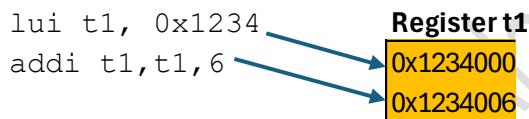

| Figure 2-4 Using lui and addi to generate a 32-bit immediate value. ....                      | 2-10 |

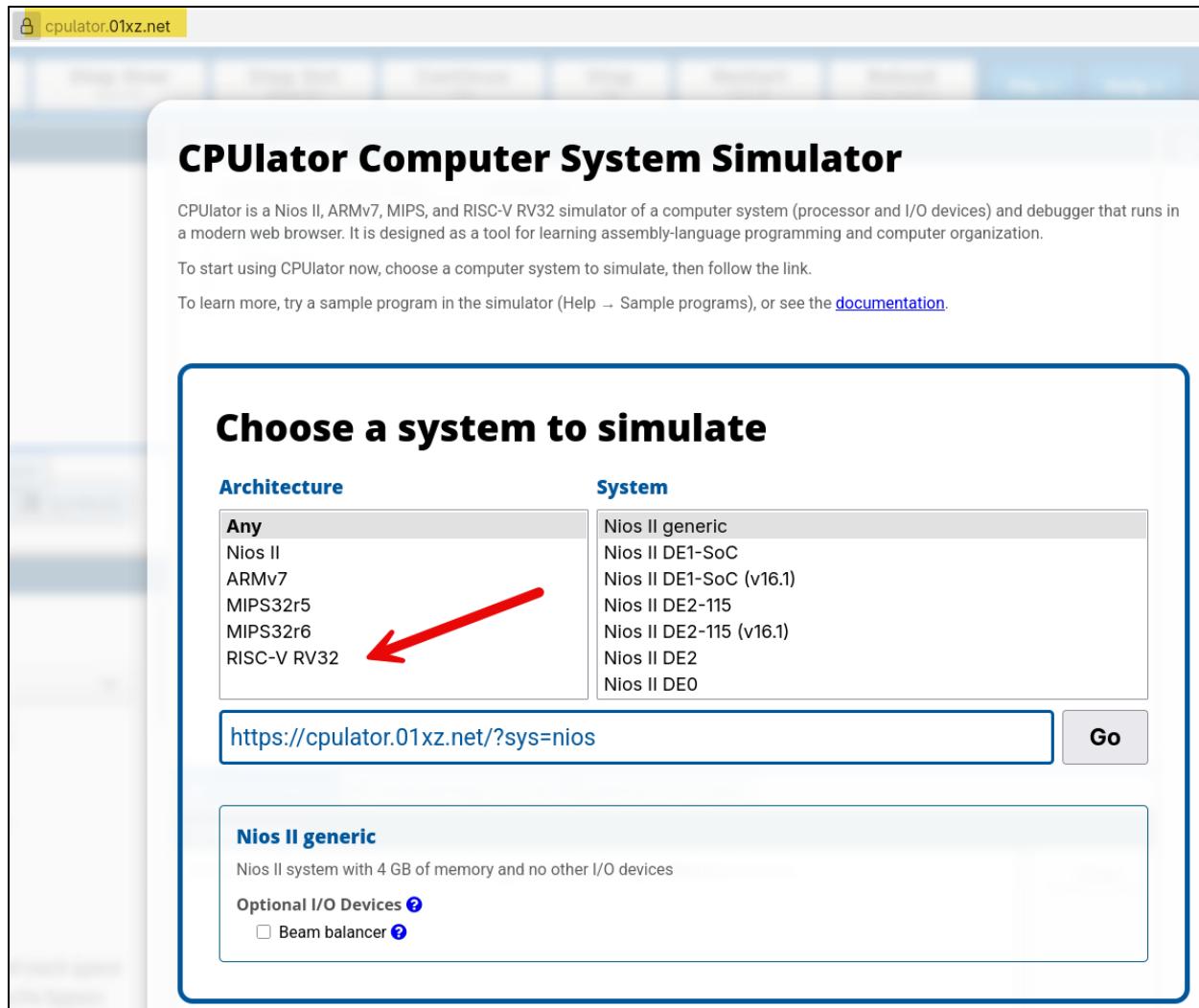

| Figure 2-5 CPULator home page .....                                                           | 2-34 |

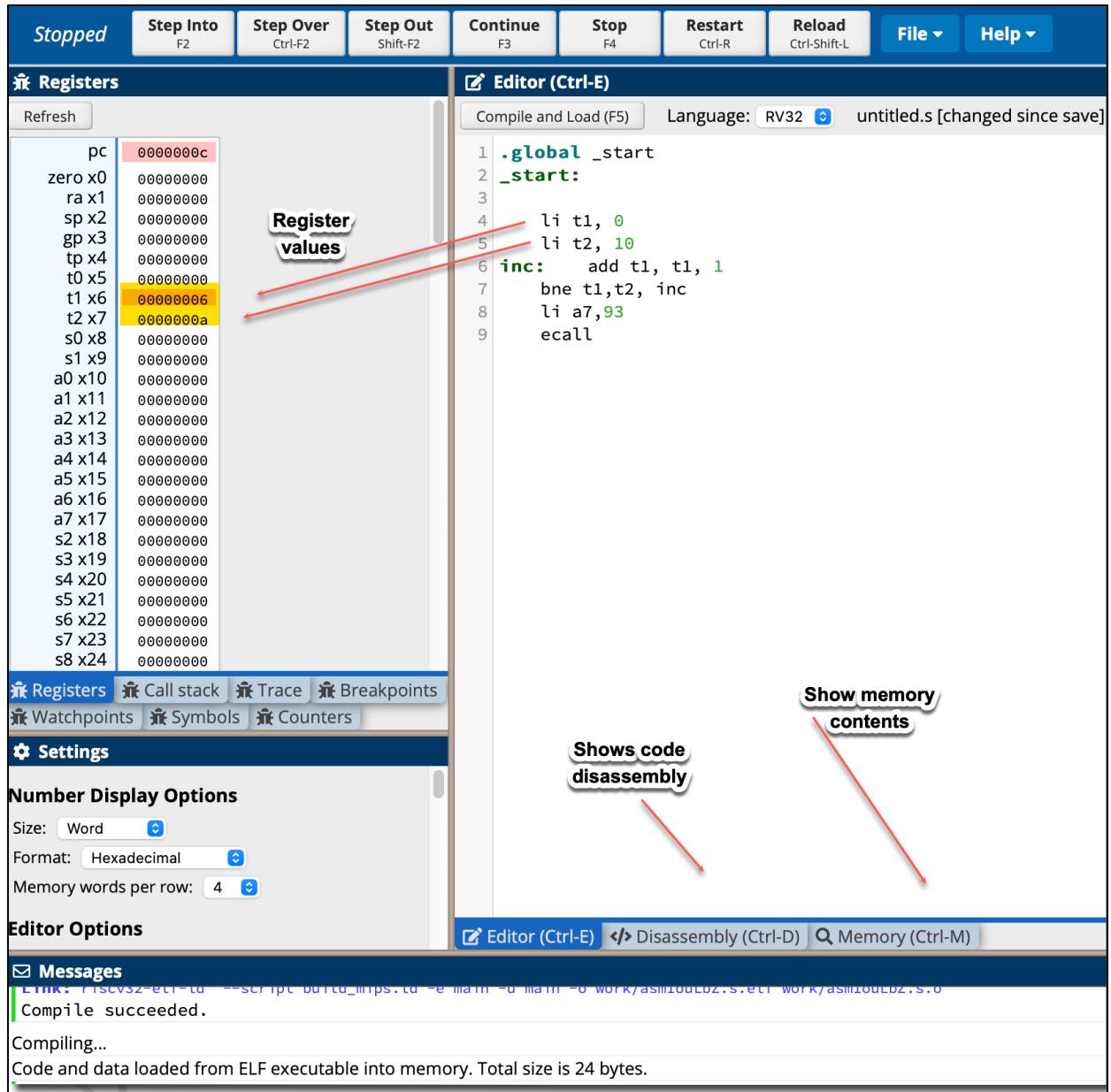

| Figure 2-6 Compiling and executing code with CPULator .....                                   | 2-35 |

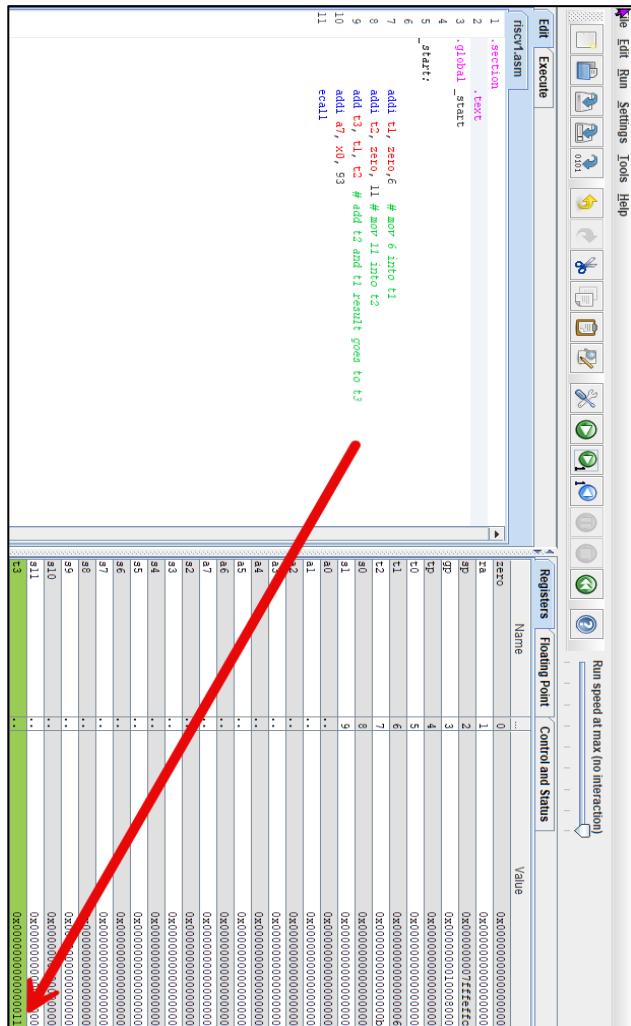

| Figure 2-7 RARS Execution screen .....                                                        | 2-36 |

| Figure 2-8 Downloading RARS.....                                                              | 2-37 |

| Figure 3-1 GDB trace of listing3-1 .....                                                      | 3-5  |

| Figure 3-2 AUIPC and ADDI instruction example to generate an address .....                    | 3-9  |

| Figure 3-3 GDB using TUI .....                                                                | 3-21 |

| Figure 4-1 ADD and ADDW instructions .....                                                    | 4-3  |

| Figure 4-2 Calculating LI to, 0xffffdc5678 non-aliased steps.....                             | 4-6  |

| Figure 4-3 Illustrating the add and addiw instructions .....                                  | 4-7  |

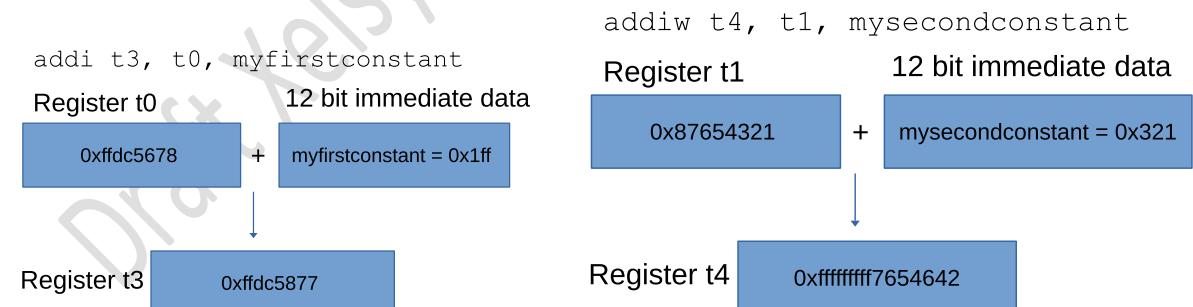

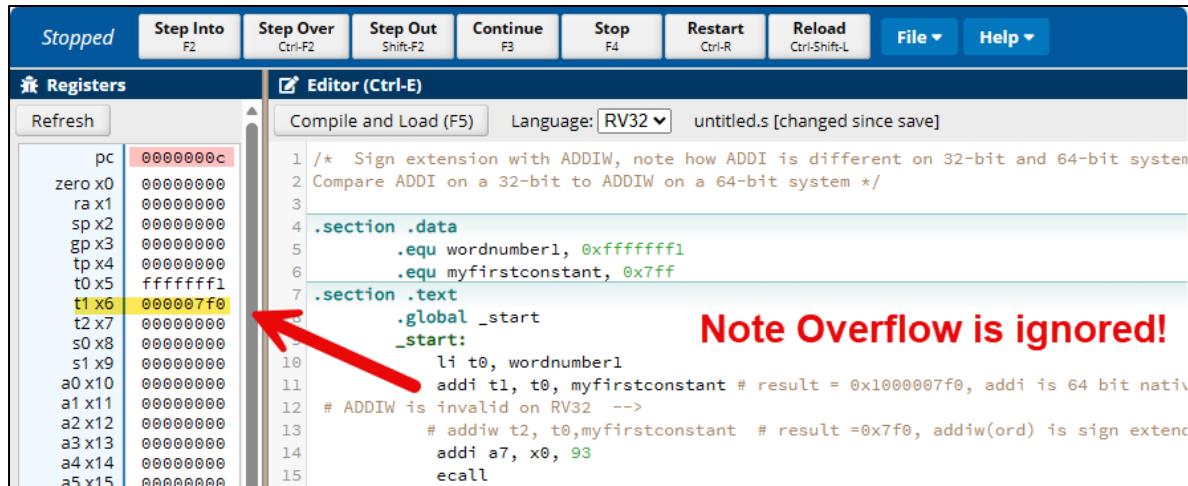

| Figure 4-4 GDB trace comparing ADD (64-bit) with ADDIW (64-bit) .....                         | 4-9  |

| Figure 4-5 Comparing ADDI on a 32-bit system to ADDIW on a 64-bit system .....                | 4-10 |

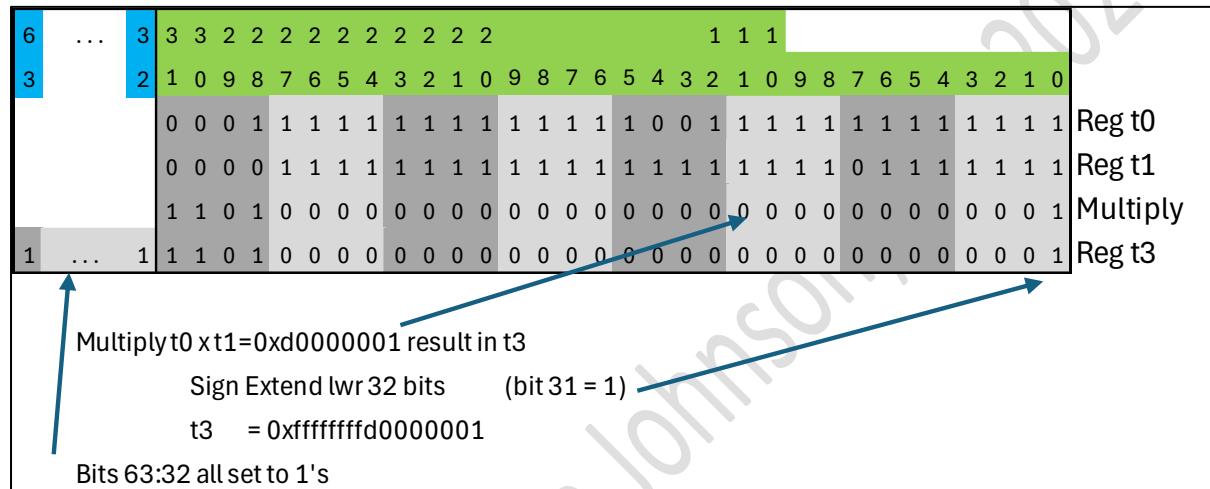

| Figure 4-6 MULW instruction.....                                                              | 4-17 |

| Figure 4-7 Using a manual long multiplication method to multiply two 64-bit hex numbers ..... | 4-18 |

| Figure 4-8 SLL instruction sll t2, t0, t1.....                                                | 4-22 |

| Figure 4-9 GDB trace of Listing 4-10 .....                                                    | 4-23 |

| Figure 5-1 Breakdown of blt instruction .....                                                 | 5-2  |

| Figure 5-2 Bit breakdown of JAL instruction .....                                             | 5-3  |

| Figure 5-3 Program flow of makesquares listing .....                                          | 5-5  |

| Figure 6-1 Stack contents operations .....                                                    | 6-2  |

|                                                                                            |      |

|--------------------------------------------------------------------------------------------|------|

| Figure 6-2 Part one of Listing 6-11's program flow.....                                    | 6-22 |

| Figure 6-3 Part two of Listing 6-11's program flow.....                                    | 6-23 |

| Figure 7-1 Using GDB with GCC.....                                                         | 7-22 |

| Figure 8-1 Floating-point registers.....                                                   | 8-2  |

| Figure 8-2 FADD bit fields .....                                                           | 8-5  |

| Figure 8-3 <b>FCSR</b> bit definitions.....                                                | 8-5  |

| Figure 8-4 Field breakdown of FADD.s f2,f0,f, rtz instruction.....                         | 8-6  |

| Figure 8-5 GDB showing floating-point number classification .....                          | 8-19 |

| Figure 8-6 Annotated instruction steps to generate a subnormal number.....                 | 8-20 |

| Figure 9-1 Vtype register bit fields.....                                                  | 9-4  |

| Figure 9-2 Using the CSRR instruction to view Vector CSR values.....                       | 9-5  |

| Figure 9-3 Simultaneous addition of multiple array elements .....                          | 9-6  |

| Figure 9-4 GDB showing vector elements.....                                                | 9-8  |

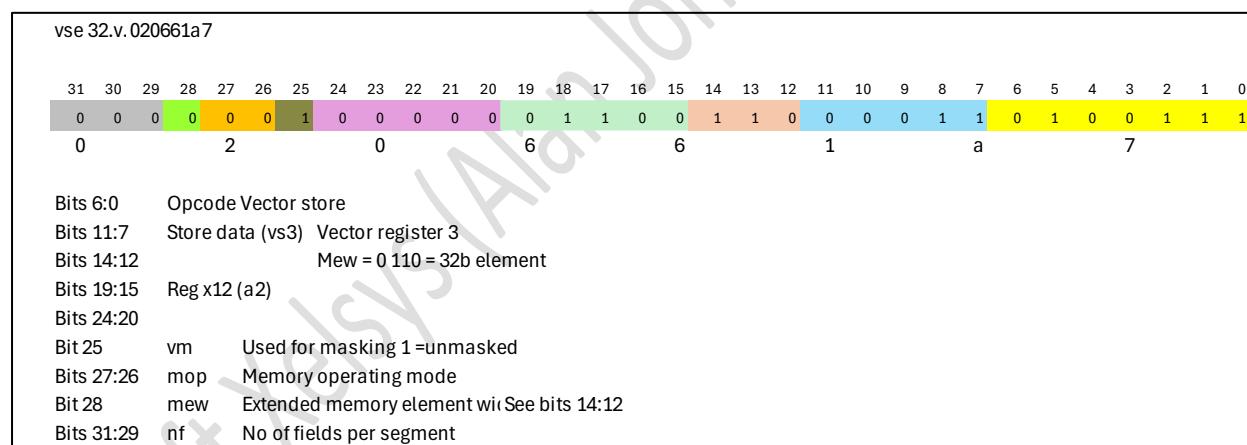

| Figure 9-5 Bit field breakdown for vector store instruction .....                          | 9-9  |

| Figure 9-6 Adding a scalar to all elements of a vector.....                                | 9-10 |

| Figure 9-7 Grouping vector registers .....                                                 | 9-15 |

| Figure 9-8 Loading two vector registers with one instruction.....                          | 9-17 |

| Figure 9-9 Operating on two vector registers with a single add instruction .....           | 9-18 |

| Figure 9-10 CSR registers after execution of the vsetivli t0, 16, e32, m2 instruction..... | 9-18 |

## Tables

|                                                                    |      |

|--------------------------------------------------------------------|------|

| Table 1-1 Binary, Decimal and Hexadecimal equivalents .....        | 1-4  |

| Table 1-2 Converting decimal to binary .....                       | 1-9  |

| Table 1-3 Signed number representation .....                       | 1-11 |

| Table 1-4 Signed and unsigned numbers .....                        | 1-12 |

| Table 1-5 Data type sizes .....                                    | 1-14 |

| Table 1-6 Double-Dabble example .....                              | 1-20 |

| Table 1-7 Three digit double dabble example .....                  | 1-21 |

| Table 1-8 Floating-Point formats .....                             | 1-22 |

| Table 1-9 BIAS within single precision IEEE 754 .....              | 1-23 |

| Table 1-10 Truth table - AND .....                                 | 1-26 |

| Table 1-11 Truth table - OR .....                                  | 1-26 |

| Table 1-12 Truth table - XOR .....                                 | 1-26 |

| Table 1-13 Simple example of encoding text using XOR .....         | 1-27 |

| Table 2-1 Base integer instruction set variants .....              | 2-3  |

| Table 2-2 Caller/Callee Responsibility for X registers .....       | 2-5  |

| Table 2-3 Bit fields of the addi I-type instruction .....          | 2-7  |

| Table 2-4 Bit fields of the add R-Type instruction .....           | 2-7  |

| Table 2-5 Bit fields of the sw S-Type instruction .....            | 2-8  |

| Table 2-6 AUIPC example .....                                      | 2-9  |

| Table 2-7 LUI example .....                                        | 2-9  |

| Table 2-8 Bit fields of the auipc U-Type instruction .....         | 2-10 |

| Table 2-9 Bit fields of the B-Type instruction .....               | 2-11 |

| Table 2-10 Bit fields of the J-Type instruction .....              | 2-12 |

| Table 2-11 Funct field usage with instruction types .....          | 2-13 |

| Table 2-12 Funct fields used for R-Type Integer instructions ..... | 2-13 |

| Table 2-13 GNU Tools associated with assembling and linking .....  | 2-14 |

| Table 2-14 Assembly language sections .....                        | 2-15 |

| Table 2-15 Commonly used GDB commands .....                        | 2-22 |

|                                                                                  |      |

|----------------------------------------------------------------------------------|------|

| Table 3-1 Using GDB to display memory contents .....                             | 3-2  |

| Table 3-2 Parameters required by the Write syscall.....                          | 3-6  |

| Table 3-3 Parameters required by the read syscall .....                          | 3-7  |

| Table 3-4 Absolute and relative addressing.....                                  | 3-10 |

| Table 3-5 Comparison of relaxed and non-relaxed code.....                        | 3-15 |

| Table 4-1 Data Types.....                                                        | 4-1  |

| Table 4-2 Sign extension example .....                                           | 4-5  |

| Table 4-3 Detecting an overflow condition (signed).....                          | 4-13 |

| Table 4-4 Detecting an overflow condition (unsigned) .....                       | 4-13 |

| Table 4-5 Summary of RVM Multiply Instructions.....                              | 4-18 |

| Table 4-6 RV32 Shift Instructions.....                                           | 4-21 |

| Table 4-7 RISC-V Logical Instructions.....                                       | 4-24 |

| Table 5-1 Conditional branch instructions.....                                   | 5-2  |

| Table 7-1 C optimization levels.....                                             | 7-6  |

| Table 7-3 Inline assembly template .....                                         | 7-16 |

| Table 7-3 printf format specifiers .....                                         | 7-20 |

| Table 8-1 Bit fields of single and double precision floating-point numbers ..... | 8-3  |

| Table 8-2 Floating-point register width .....                                    | 8-3  |

| Table 8-3 Field meaning of FADD.s instruction.....                               | 8-5  |

| Table 8-4 Rounding mode bits .....                                               | 8-6  |

| Table 8-5 Floating-point comparison instructions.....                            | 8-16 |

| Table 8-6 Floating-point classes.....                                            | 8-17 |

| Table 9-1 Vector CSRs .....                                                      | 9-3  |

| Table 9-2 Vtype SEW bit meaning.....                                             | 9-3  |

| Table 9-3 LMUL and grouping correspondence.....                                  | 9-14 |

| Table 10-1 Spike interactive commands for debugging.....                         | 10-8 |

## *Listings*

|                                                                       |      |

|-----------------------------------------------------------------------|------|

| Listing 2-1 Assembly code example .....                               | 2-14 |

| Listing 2-2 Interacting with assembly sections. ....                  | 2-16 |

| Listing 3-1 Basic read (load) and write (store) memory operation..... | 3-3  |

| Listing 3-2 Use of the Write Syscall .....                            | 3-6  |

| Listing 3-3 Input operation.....                                      | 3-7  |

| Listing 3-4-Relative addressing example.....                          | 3-10 |

| Listing 3-5 Using absolute addressing with %lo and %hi .....          | 3-11 |

| Listing 3-6 Non relaxed version of code.....                          | 3-12 |

| Listing 3-7 Relaxed version of code.....                              | 3-13 |

| Listing 3-8 Further example of linker relaxation use .....            | 3-17 |

| Listing 4-1 ADD and ADDW instructions .....                           | 4-2  |

| Listing 4-2 ADDi example .....                                        | 4-7  |

| Listing 4-3 MV instruction .....                                      | 4-11 |

| Listing 4-4 Use of SUB and SUBW instructions .....                    | 4-12 |

| Listing 4-5 Multiply instructions on RV32 .....                       | 4-14 |

| Listing 4-6 64-bit multiplication .....                               | 4-15 |

| Listing 4-7 Further Multiply instructions on RV64 .....               | 4-16 |

| Listing 4-8 Division example.....                                     | 4-19 |

| Listing 4-9 Further Division examples .....                           | 4-19 |

| Listing 4-10 Shift instructions.....                                  | 4-22 |

| Listing 4-11 Logical Instructions (RV64) .....                        | 4-24 |

| Listing 5-1 Squaring numbers from 1 to 20.....                        | 5-3  |

| Listing 6-1 Allocation and deallocation of the stack .....            | 6-2  |

| Listing 6-2 Nested routines example.....                              | 6-4  |

| Listing 6-3 main.s .....                                              | 6-6  |

| Listing 6-4 squareit.s .....                                          | 6-9  |

| Listing 6-5 Makefile for squareit .....                               | 6-10 |

| Listing 6-6 Callerprogram.....                                        | 6-12 |

| Listing 6-7 Called program .....                                      | 6-12 |

|                                                                                           |      |

|-------------------------------------------------------------------------------------------|------|

| Listing 6-8 Macro example (callmacro.s) .....                                             | 6-13 |

| Listing 6-9 called macro program (printmacro.s).....                                      | 6-14 |

| Listing 6-10 Internal Macro used to print newline character for the squares program ..... | 6-15 |

| Listing 6-11 Using the stack with the squares program.....                                | 6-18 |

| Listing 6-12 Main program passing a sting to be printed .....                             | 6-24 |

| Listing 6-13 Macro program to print string.....                                           | 6-24 |

| Listing 6-14 Push Macro.....                                                              | 6-31 |

| Listing 6-15 Pop Macro .....                                                              | 6-31 |

| Listing 6-16 Using the push and pop macros .....                                          | 6-31 |

| Listing 7-1 Basic C program .....                                                         | 7-2  |

| Listing 7-2 C program with user input.....                                                | 7-8  |

| Listing 7-3 C program calling an external assembly routine .....                          | 7-9  |

| Listing 7-4 RISC-V multiply function called from C.....                                   | 7-9  |

| Listing 7-5 Basic ASM example.....                                                        | 7-15 |

| Listing 7-6 Extended ASM example.....                                                     | 7-16 |

| Listing 7-7 Further BASIC asm example .....                                               | 7-18 |

| Listing 7-8 Using the printf function with assembly code.....                             | 7-20 |

| Listing 8-1 Adding two double-precision floating-point numbers .....                      | 8-7  |

| Listing 8-2 Floating-point rounding using static modes .....                              | 8-9  |

| Listing 8-3 Using dynamic rounding mode.....                                              | 8-11 |

| Listing 8-4 Use of sqrt instruction and reading the FCSR register .....                   | 8-13 |

| Listing 8-5 Classification of numbers - subnormal and quiet NaN.....                      | 8-18 |

| Listing 9-1 Vector to vector addition/subtraction .....                                   | 9-6  |

| Listing 9-2 Adding a vector and a scalar .....                                            | 9-10 |

| Listing 9-3 Use of vector vslide instructions.....                                        | 9-12 |

| Listing 9-4 Grouping vector registers .....                                               | 9-15 |

| Listing 9-5 Use of vmerge instruction .....                                               | 9-18 |

# Chapter 1. The fundamentals of assembly language.

## Overview of the chapter

Chapter 1 lays the foundation for understanding assembly language. The focus is on general principles which are essential prior to delving into the specifics of RISC-V. Topics include the purpose, structure, and advantages of assembly programming, and introduces the number systems and logic operations that underpin low-level code.

### 1.1. What is assembly language?

Assembly language is a computer language that is much closer to the operation of the computer itself. Today most of the coding is performed using languages that are easier for humans to understand, as far as assembly language goes the coding language uses *abbreviations* to give an insight into the nature of the operation being performed. An example could be `bgt` which stands for branch if greater or less than (some condition)

#### 1.1.1. High-level languages Vs Assembly language

Many high-level languages place a strong emphasis on abstraction, treating functions as impenetrable black boxes and hides the inner workings. Assembly language takes a different approach and allows (indeed mandates) the coder to familiarize themselves with the innards of the system.

The former method is like a Rapid Application Development (RAD) methodology that works well with teams whereas the second approach often includes smaller groups with specialized knowledge. Both approaches have their place. Digital computers inherently process data in one of two states (binary) so it is essential that we understand the low-level world of one's and zero's.

Strangely enough, assembly language programming has been gaining in popularity after a hiatus, due to the rise in higher level, object-oriented languages. This comeback may be attributed to the rapid development of robotics, self-driving cars and other autonomous devices that require sensors reacting to real-time events. It is envisaged that assembly language programmers will be in higher demand during the coming decade.

#### 1.1.2. Architecture and Machine code

Processors have different *architectures*, and they each understand their own *machine code* instructions – at their very heart these instructions are combinations of binary numbers that instruct the processor how to proceed. Binary numbers are cumbersome for human operators and instead a set of *mnemonic* instructions are used. A hypothetical example could be an instruction such as `add r1, r2, r3` which would add two numbers together that are contained in register2<sup>3</sup> and register3, placing the result in register1 or `add r1, r2, 45` which could add the value 45 to the value contained in register2, placing

<sup>3</sup> Registers are low-capacity, high-speed storage elements, (typically anywhere from one to eight bytes in size) contained within the processor architecture.

the result in register1. The corresponding native machine code (again hypothetical) could be the binary code 10101100 00010010 00101100. The *mnemonic* instructions make up the *assembly language*.

### 1.1.3. Assembling, compiling and linking

The role of the *assembler* (program) is to convert programmer-readable assembly instructions into the corresponding machine code instructions. The output code is termed an *object* file. Conversely a *disassembler* converts machine code instructions back into assembly language. The assembler has additional roles such as understanding a set of *directives* that can define and place data into the computer's memory locations. An example could be a set of error codes defined as textual informational messages. These messages are defined by the programmer rather than the specific processor itself. There are a number of these directives, and they will be discussed in more detail as the document progresses.

Higher-level languages use *compilers* to translate to machine code. After the assembly or compilation process the object files are *linked* to form an executable program. The *linker* may act on individual or multiple files. High level language instructions do not normally have a one-to-one correspondence with the underlying machine code instructions. They are designed to be more instinctive to the programmer by providing English like keywords such as *if ..then*, *while*, and *print*. High level languages can be *interpretive* and translated into machine code instructions during runtime, or pre-compiled before runtime into native machine-code.

### 1.1.4. Pseudocode

Pseudocode is used prior to writing *real, syntactically*<sup>4</sup> *correct* code. It outlines a set of algorithmic instructions, describing the program flow at a higher level. The benefit is to focus and plan the tasks ahead without getting too involved in low-level syntactical details, though *logic errors* may still persist. The flow is typically Algorithm → Pseudocode → Actual computer code.

Although pseudocode is not strictly defined, keywords such as IF-THEN, WHILE, GREATER THAN, . . . , are used to define program-flow.

### 1.1.5. Why use assembly?

Assembly language has a direct relationship with the CPU that it is running on and as a result the programs will be more compact and efficient. It is also more suited to *system-level* programming. A disadvantage is that many lines of code may be required when compared to high level languages and as a result a hybrid approach may be deployed where the bulk of the code could be written using C or Python which can pass parameters *to* and accept return values *from* a smaller section of assembly code. Portability is also an issue since the assembly language is tightly coupled with the CPU that it is running on.

---

<sup>4</sup> The syntax of a language is the grammatical structure of a language. Computer languages usually have a very formal structure, with the precise order of objects used in a command strictly defined. The statement "an orange has blue skin" is syntactically correct but not semantically correct.

In the interests of education, this book will focus more on “pure” assembly coding rather than the pragmatic hybrid approach<sup>5</sup>.

Experienced system-level coders may wish to skip this chapter or simply skim through it and treat it as a refresher. The material discussed in *this* chapter is general and does not necessarily apply to any specific system.

### 1.2. Hardware Vs Software Vs Firmware

#### 1.2.1. Hardware

In computer terms *hardware* refers to the physical components that make up the system. Hardware is something that can be seen and touched.

#### 1.2.2. Software

*Software* refers to the actual instructions that are loaded into the computer’s memory. These instructions may direct the hardware to perform certain tasks. For example, the system software is responsible for displaying the result of an operation onto a hardware output device such as a display screen or printer and for taking input from a device such as a keyboard. In general, though, software is a set of instructions that cause an operation to occur such as adding two numbers together.

#### 1.2.2.1. Firmware

*Firmware* can be thought of as a set of instructions residing in hardware. This definition has become somewhat blurred as these instructions were originally loaded onto read only devices (ROMs). These devices would be physically replaced when new upgrade code was required. Over time Erasable Programmable integrated circuits (IC’s) (EPROMs) were introduced, which as the name implies could be written over with new code. Today, non-volatile random-access memory (NVRAM) devices are used and can often be upgraded on-line without even requiring a reboot. This process is sometimes referred to as *flashing* since the underlying device is often Flash memory.

## 1.3. Number Systems

Anthropologists may make a claim that we count in base 10 as this is the number of digits on our hands. Other cultures have used base 60 and base 20 (possibly using both fingers and toes). These number systems are not as well suited to computer systems and today<sup>6</sup> base 2 and base 16 dominate when using low-level assembly programming.

#### 1.3.1. Binary, Octal, Hexadecimal

Consider the base 10 number  $4673_{10}$  – this breaks down into:

<sup>5</sup> That is not to say that hybrid programming will be ignored within this text.

<sup>6</sup> Base 8 - Octal was also used on many earlier computers such as Digital Equipment Corporation’s PDP family of minicomputers.

$$\begin{aligned}

& 4 \times 10^3 \\

& + \\

& 6 \times 10^2 \\

& + \\

& 7 \times 10^1 \\

& + \\

& 3 \times 10^0 \\

& = 4000 + 600 + 70 + 3 = 4673

\end{aligned}$$

The use of ten (0-9) different characters along with their position represented a major advance in computation when compared to systems such as the Roman counting method.

Digital electronic systems naturally gravitate towards a two-state binary system where current either flows or it does not. These two states are represented by the symbols 0 or 1.

Each binary digit is termed a *bit*(b). For convenience binary digits are often grouped into 8 bits termed a *Byte*(B). Since eight bits can represent numbers ranging from 00000000 through 11111111, the decimal values translate to 0 through 255. A disadvantage of binary numbers is that a three-digit decimal number may require an equivalent of up to ten binary digits. A more compact numbering system is base 16 (hexadecimal) which treats a group of four binary numbers as a single hexadecimal number. This means that two hexadecimal numbers will represent a single byte<sup>7</sup>. Hexadecimal numbers use the same symbols as decimals up to the value 9, then use the characters A through F to represent decimal numbers ten through fifteen. The hex number 10<sub>16</sub> corresponds to decimal number 16<sub>10</sub>.

Table 1-1 Binary, Decimal and Hexadecimal equivalents

| Binary | Decimal | Hexadecimal |

|--------|---------|-------------|

| 0000   | 0       | 0           |

| 0001   | 1       | 1           |

| 0010   | 2       | 2           |

| 0011   | 3       | 3           |

| 0100   | 4       | 4           |

| 0101   | 5       | 5           |

| 0110   | 6       | 6           |

| 0111   | 7       | 7           |

<sup>7</sup> A single hexadecimal number is sometimes referred to as a nibble.

|             |    |   |

|-------------|----|---|

| <b>1000</b> | 8  | 8 |

| <b>1001</b> | 9  | 9 |

| <b>1010</b> | 10 | A |

| <b>1011</b> | 11 | B |

| <b>1100</b> | 12 | C |

| <b>1101</b> | 13 | D |

| <b>1110</b> | 14 | E |

| <b>1111</b> | 15 | F |

### 1.3.2. Converting Binary to Decimal

Each binary<sup>8</sup> digit can be converted to decimal by multiplying its value by two raised to an index where the index corresponds to the bit's position.

The binary number  $110101_2$  then, can be converted to decimal using the following steps.

$$1 \times 2^5 + 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 =$$

$$32 + 16 + 0 + 4 + 0 + 1 \\ = 53_{10}$$

#### 1.3.2.1. General rule for base conversion

Any number  $n$  in binary can be written as:

$$n = 10 \times \text{quotient} + \text{remainder}$$

#### 1.3.2.2. Binary long division

Example:  $n = 101101$

<sup>8</sup> Note these steps use pure binary, it is often faster to temporarily use decimal numbers as interim steps, for example to find out the largest divisor that divides  $1010_2$  into binary  $10111010_2$ , convert the numbers to decimal to get  $10_{10}$  and  $186_{10}$ , so it is easy to see that  $18_{10}$  is the largest number when multiplied by  $10_{10}$  that will divide into  $186_{10}$ . Converting  $18_{10}$ , back to binary gives  $10010_2$ . Checking  $100010_2 \times 1010_2 = 10110100_2$  which divides into  $10111010_2$

Numerator  $\div$  Denominator = Quotient + Remainder

Numerator  $\rightarrow$  the number being divided

Denominator  $\rightarrow$  the number you divide by

Quotient  $\rightarrow$  the result of the division

Remainder  $\rightarrow$  what's left over

$$1 \ 0 \ 1 \ 1 \ 0 \ 1 = 10 \times \text{Quotient} + \text{Remainder}$$

so divide by the target base which is 10

$$1 \ 0 \ 1 \ 1 \ 0 \ 1 \div 1 \ 0 \ 1 \ 0 \text{ (10 decimal in binary)}$$

|            |   |   |   |   |   |   |

|------------|---|---|---|---|---|---|

| Quotient > | 0 | 0 | 0 | 1 | 0 | 0 |

| 1          | 0 | 1 | 0 | 1 | 0 | 1 |

|            | 1 | 0 | 1 | 0 |   |   |

|            | 1 | 0 | 1 | 0 |   |   |

|            | 0 | 0 | 0 | 1 |   |   |

|            | 0 | 0 | 0 | 1 | 0 |   |

| Remaind >  | 0 | 0 | 0 | 1 | 0 | 1 |

subtracted

Bring down the next digit from the numerator

Doesn't divide so bring down the next digit and place 0 in the next quotient position

Still does not divide, place 0 in the next quotient position and

this is the remainder as there are no more numerator digits

This gives a quotient of 4 with a remainder of 5

Verifies  $n = \text{Base} \times \text{Quotient} + \text{Remainder}$

### 1.3.2.3. Repeated division method (algorithmic)

- Divide by target base – Here base = 10

- With repeated division the remainders are the decimal digits.

- The decimal numbers appear in reverse order with the least significant appearing first.

#### Example

Convert:  $1111001_2$  to decimal by dividing by  $1010_2$  ( $10_{10}$ )

Repeatedly divide by  $1010_2$ ; each remainder is one decimal digit (in binary).

Divide:

$$1111001_2 \div 1010_2$$

Using trial and error - test multiples of  $1010_2$ :

$$\text{Attempt } 1010_2 \times 1011_2 = 1101110_2$$

This divides into  $1111001_2$  so try next number up -

$$1010_2 \times 1100_2 = 1111000_2, \text{ this also divides so try next number}$$

$$1010_2 \times 1101_2 = 100000010_2, \text{ too big so } 1100_2 \text{ is the quotient}$$

Now subtract (the product of the base by the largest divisor) from the number that is to be converted to get the quotient.

$$\begin{array}{r} 1111001 \\ - 1111000 \\ \hline 0000001 \end{array}$$

Quotient =  $1100_2$  (It divided 1100 times)

Remainder =  $1_2 1_{10}$

Now divide the quotient by the base  $1100 \div 1010_2$

$$\begin{array}{r} 1100 \\ - 1010 \\ \hline 0010 \end{array}$$

Quotient=1 It divided 1 time

Remainder =  $10_2 2_{10}$

Now divide the quotient by the base  $1 \div 1010$

It did not divide

Quotient = 0

Remainder =  $1_2 1_{10}$

List the remainders in reverse order =  $121_{10}$

### Further example

Convert  $10101001$  to decimal

$$1010 \times 10000 = 10100000$$

$$\begin{array}{r} 10101001 \\ - 10100000 \\ \hline 00001001 \end{array}$$

Remainder =  $9_{10}$

$10000$  (Quotient)

Divide Quotient by the base  $10000 \div 1010$

10000

- 01010

0 1 10

Remainder = 6<sub>10</sub>

Quotient is 1

Divide quotient by the base 1 ÷ 1010

Divides zero times with 1 left over

Remainder = 1<sub>10</sub>Assemble the remainders in reverse order = 169<sub>10</sub>

**Note there are easier ways to perform these calculations, but the steps presented can be adapted to assembly programming in a more algorithmic method.**

#### 1.3.2.4. Converting Decimal to Binary

The following method breaks down a decimal number into powers of two, so to convert the number 843<sub>10</sub> to its equivalent binary number –

1. First get the highest power of two contained in 843 which is 512 ( $2^9$ ).

2. Subtract 512 from 843 = 331,

3. The highest power of two contained in 331 is 256 ( $2^8$ ),

4. Subtract 256 from 331 to get 75,

5. The highest power of two contained in 75 is 64 ( $2^6$ ),

6. Subtract 64 from 75 to get 11,

7. The highest power of two contained in 11 is 8( $2^3$ ),

8. Subtract 8 from 11 to get 3,

9. The highest power of two contained in 3 is 2 ( $2^1$ ),

10. Subtract from 3 to get 1,

11. The highest power of two contained in 1 is 1 ( $2^0$ ),

12. Subtract 1 from 1 to get 0.

Everywhere that a power of two appears, write its index as the binary value one and where it did not appear write the binary value zero using the positional notation shown in Table 1-2.

Table 1-2 Converting decimal to binary

| Value       | 1     | 1     | 0     | 1     | 0     | 1     |

|-------------|-------|-------|-------|-------|-------|-------|

| Position    | 5     | 4     | 3     | 2     | 1     | 0     |

| Multiply by | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ |

Another way of converting is a repeated division method. Divide the number repeatedly until zero is reached. Take note of the remainders and put the first remainder in the left-most position, then the second remainder into the left-most second position, repeating until all reminders have been recorded.

Figure 1-1 Converting Decimal to binary using repeated division by  $2_{10}$

$$\begin{array}{r}

2\overline{)843} \\

2\overline{)421} \text{ Rem 1} \\

2\overline{)210} \text{ Rem 1} \\

2\overline{)105} \text{ Rem 0} \\

2\overline{)52} \text{ Rem 1} \\

2\overline{)26} \text{ Rem 0} \\

2\overline{)13} \text{ Rem 0} \\

2\overline{)6} \text{ Rem 1} \\

2\overline{)3} \text{ Rem 0} \\

2\overline{)1} \text{ Rem 1} \\

2\overline{)0} \text{ Rem 1}

\end{array}$$

Now write down the remainder starting from the *top* to get:

1101001011<sub>2</sub>.

|       |       |       |       |       |       |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| $2^9$ | $2^8$ | $2^7$ | $2^6$ | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ |

| 1     | 1     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | 1     |

### 1.3.3. Converting Hexadecimal to Decimal

A hex number such as  $5B7C_{16}$  can be converted to decimal using a power of sixteen method –

$$= 5 \times 16^3 + B \times 16^2 + 7 \times 16^1 + C \times 16^0$$

$$= 20,480 + 2816 + 112 + 12$$

$$= 23420$$

**1.3.4. Converting Decimal to Hexadecimal**

Take the number as shown, divide repeatedly by  $16_{10}$  until zero is reached. Record the remainders in base 16 format (e.g. for a remainder of  $10_{10}$ , record "A"). Note the remainders and put the last remainder in the left-most position, the second from last remainder into the left-most second position, repeating until all remainders have been recorded.

Figure 1-2 Converting Decimal to binary using repeated division by  $16_{10}$

$$\begin{array}{r}

16 \overline{)23420} \\

16 \overline{)1463 \text{ Rem C}} \\

16 \overline{)91 \text{ Rem 7}} \\

16 \overline{)5 \text{ Rem B}} \\

16 \overline{)0 \text{ Rem 5}}

\end{array}$$

Again, printing out the remainders from the bottom gives 5B7C

**1.3.5. Binary Fractions**

The binary numbers that have been dealt with up to this point are *natural* number equivalents (positive whole numbers). Positional notation is used to show the corresponding power of two index.<sup>9</sup> Fractions can be represented in binary by moving to the left of the  $2^0$ . These values then become  $2^{-1}$ ,  $2^{-2}$ , ...

**1.3.6. Converting a binary fraction to decimal**

$1101.01$  is equivalent to the base 10 number  $13.25$  since we have:

$$1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2}$$

**1.3.6.1. Converting a decimal fraction to binary.**

Repeatedly multiply the fractional part by two until it becomes zero, taking note of the value to the left (integer portion) of the decimal point. Accumulate the values of the integer part from top to bottom to get the binary fractional part.

Example  $0.625_{10}$

$$0.625 \times 2 = 1.25$$

$$0.25 \times 2 = 0.5$$

$$0.5 \times 2 = 1.0$$

Stop since the value to the right of the decimal point = 0

Take the integer value from top to bottom =  $0.101_2$

<sup>9</sup> Recall that negative indices can be resolved by changing the sign of the index and changing the operation from division to multiplication and vice versa so that  $1 / 2^2$  becomes  $1 \times 2^2 = 4$  and  $4 \times 2^2 = 4/2^2 = 16$

Consider number 0.3

$$0.3 \times 2 = 0.6$$

$$0.6 \times 2 = 1.2$$

$$0.2 \times 2 = 0.4$$

$$0.4 \times 2 = 0.8$$

$$0.8 \times 2 = 1.6$$

$$0.6 \times 2 = 1.2$$

$$0.2 \times 2 = 0.4$$

$$0.4 \times 2 = 0.8$$

$$0.8 \times 2 = 1.6$$

$$0.6 \times 2 = 1.2$$

This highlighted value has been met before, so this is a recurring fraction with the pattern 0011 repeating - .0100110011... This means that when evaluating, a halt counter should be added. The logic would be to end when the fractional part = 0 or when the required degree of precision has been reached.

### 1.3.7. One and Two's complement

An eight-bit byte can represent any one of 256 values ranging from 0 – 255<sub>10</sub>. This is known as *unsigned* notation. Another representation is to use half of the range as positive integers and the other half as negative, in this case the range is from +127<sup>10</sup> through -128. This method uses the *most significant bit* to represent the sign and is known as *signed* notation. The number line for an eight-bit signed number is:

-128, -127, ..., 0, 1, 2, ..., 127

Table 1-3 Signed number representation.

| $2^7$    | $2^6$          | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ |

|----------|----------------|-------|-------|-------|-------|-------|-------|

| Sign bit | Magnitude Bits |       |       |       |       |       |       |

Interpreting the value of a signed number is straightforward –

The procedure is to add the corresponding powers of two of each bit's place value but leave out the sign bit. The next step is to add in the value of the sign bit. For positive numbers it makes no difference since the value of the sign bit is zero, but for negative numbers the value of the sign bit is -128.

Example

<sup>10</sup> Zero is treated as a positive number here

- Take the positive binary number 00101100

- Add the magnitude bits together

$$0 \times 2^6 + 1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 0 \times 2^0$$

$$= 32 + 8 + 4 = 44$$

- Add in the value of the sign bit ( $2^7$ ) to get:-

$$0 + 44 = 44$$

- For the negative number 10011001

- Add the magnitude bits together.

$$0 \times 2^6 + 0 \times 2^5 + 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$$

$$= 16 + 8 + 1 = 25$$

- Add in the value of the sign bit ( $2^7$ ) to get

$$-128 + 25 = -103$$

Converting from a signed number to an unsigned number is a simple operation, the procedure is to invert the bits and then add the binary value 1.

So, to convert the positive number  $63_{10}$  to negative  $63_{10}$ .

- Convert the number to an eight-bit binary number -

00111111

- Invert the bits to get -

11000000 (one's complement)

- Add 1 to get -

11000001 (Two's complement)

- Convert back to decimal to get:-

$$-128 + 64 + 1 = 63$$

1. The first stage of inverting the bits - obtains the one's complement, adding the binary digit 1 to the one's complement - obtains the two's complement.

The following table shows an extract of the first few signed numbers.

Table 1-4 Signed and unsigned numbers

| Signed Binary Number | Decimal Equivalent |

|----------------------|--------------------|

| 0111 1111            | 127                |

|                  |      |

|------------------|------|

| <b>0111 1110</b> | 126  |

| <b>0111 1101</b> | 125  |

| .                | .    |

| <b>0000 0000</b> | 0    |

| <b>1111 1111</b> | -1   |

| <b>1111 1110</b> | -2   |

| ...              |      |

| <b>1000 0010</b> | -126 |

| <b>1000 0001</b> | -127 |

| <b>1000 0000</b> | -128 |

### 1.3.8. Addition and subtraction of binary numbers

#### 1.3.8.1. Binary Addition

To add two binary numbers together is straightforward, there are only four outcomes.

$$0 + 0 = 0$$

$$0 + 1 = 1$$

$$1 + 0 = 1$$

$$1 + 1 = 10 \text{ (0+ carry)}$$

An example of an unsigned binary addition follows-

Add 0 0 1 0 1 1 0 1 to 0 1 1 1 0 1 0 0

$$\begin{array}{r}

0 \ 0 \ 1 \ 0 \ 1 \ 1 \ 0 \ 1 \\

0 \ 1 \ 1 \ 1 \ 0 \ 1 \ 0 \ 0 \\

\hline

1 \ 0 \ 1 \ 0 \ 0 \ 0 \ 0 \ 1

\end{array}$$

Checking by adding the decimal number equivalents together –

$$45 + 116 = 161$$

Consider if these numbers being added were in signed notation – here adding two positive numbers together would result in a negative number since the sign bit of the result = 1. This is an *overflow* condition since the result of 161 is clearly outside of the maximum positive number that can be represented in signed eight-bit binary arithmetic. This is something that needs to be checked and there are conditions built-in to the processor architecture to detect this kind of situation.

Larger numbers can be dealt with by using two bytes for storage, treating the second byte as having the values  $2^8$  through  $2^{15}$ . Assemblers and compilers will refer to groups of bytes by designations such as long int, word etc. It is important to check the definitions.

One such definition is:

Table 1-5 Data type sizes

| Unit       | Width   |

|------------|---------|

| Doubleword | 64 bits |

| Word       | 32 bits |

| Halfword   | 16 bits |

| Byte       | 8 bits  |

Of course, it is important to specify signed or unsigned, again a definition for an unsigned integer in the programmer's documentation might be referred to as `uint`.

### 1.3.9. Binary subtraction

Binary subtraction can be dealt with using elementary rules for small numbers and then taking into account "borrows" rather than "carrys" but using the two's complement method described on page 1-11 is by far the preferred method for larger numbers.

The steps for binary subtraction are:

1. Obtain the two's complement of the *subtrahend* (the number that will be taken away)

2. Add this to the *minuend* (the number that will be subtracted from).

3. Add the two's complement of the subtrahend to the minuend.

4. If there is a carry after the addition, then drop the carry (final result is positive)

5. If there is no carry, then compute the two's complement of the result (final result is negative)

Taking a concrete example of subtracting  $00100100$  ( $36_{10}$ ) from  $00000010$  ( $2_{10}$ )

- Two's complement of the subtrahend

$$1101\ 1011 + 1 = 1101\ 1100$$

- Add to the minuend

|   |   |   |   |   |   |   |   |                                |

|---|---|---|---|---|---|---|---|--------------------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | Minuend                        |

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | Two's complement of subtrahend |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |                                |

(Carry = 0)

Two's complement of the result is

$$00100001 + 1 = 00100010$$

Result is negative since the carry was false = -34

Another example -

- Subtract  $45_{10}$  from  $120_{10}$

- Convert numbers to eight-bit binary

$$45_{10} = 0010 1101_2$$

$$120_{10} = 0111 1000_2$$

- Two's complement of  $00101101$

- Add to  $0111 1000$

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 |

(carry = 1)

The result is positive since carry was zero,  $01001011 = 75_{10}$

### 1.3.10. Binary multiplication

The rules for multiplication of two bits are

$$0 \times 0 = 0$$

$$0 \times 1 = 0$$

$$1 \times 0 = 0$$

$$1 \times 1 = 1$$

Note anything multiplied by zero is of course zero.

Example multiply binary 10 ( $2_{10}$ ) by 11 ( $3_{10}$ )

$$\begin{array}{r} 1 \\ 0 \end{array}$$

$$\begin{array}{r}

1 \quad 1 \quad x \\

1 \quad 0 \\

1 \quad 0 \\

1 \quad 1 \quad 0 \\

= 6_{10}

\end{array}$$

Note this is the same as decimal multiplication where we multiply by each of the digits and then add these results together.

### 1.3.11. Binary Division

The rules for division of two bits are as follows (recall that division by zero is invalid)

- $0 / 0$  invalid

- $0 / 1 = 0$

- $1 / 0$  invalid

- $1 / 1 = 1$

Division example

Divide 1 1011 (Dividend) by 00111 (Divisor)

Using long division -

|              |                          |                                                          |                      |

|--------------|--------------------------|----------------------------------------------------------|----------------------|

| Divide 11011 | by                       | 111                                                      |                      |

| 0 0 0 1 1    |                          |                                                          |                      |

| 111          | 1 1 0 1 1                | Bring down                                               |                      |

| Subtract     | <u>1 1 1</u>             | the 1                                                    |                      |

|              | 1 1 0 1                  |                                                          |                      |

| Subtract     | <u>1 1 1</u>             |                                                          |                      |

|              | 1 1 0                    | ← Remainder (since it is too small to be divided by 111) |                      |

| Check        | by converting to base 10 | 27/7                                                     | = 3 with remainder 6 |

| Dividend     | 27                       |                                                          |                      |

| Divisor      | 7                        |                                                          |                      |

| Quotient     | 3                        |                                                          |                      |

| Remainder    | 6                        |                                                          |                      |

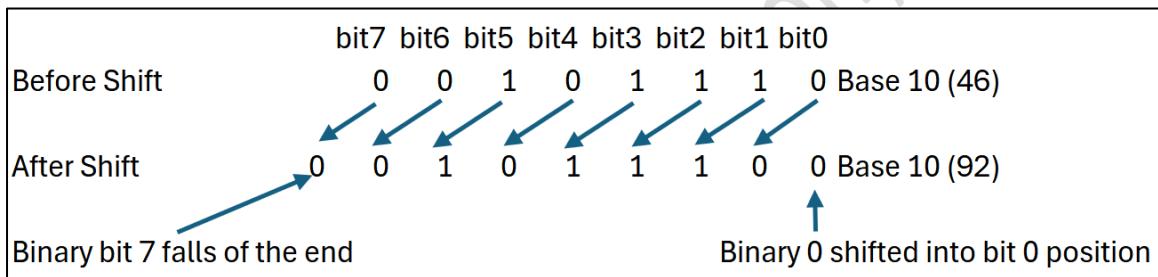

**1.3.12. Shift/ Rotate instructions to perform multiply and divide operations**

Consider an eight-bit byte 00101110 which has the decimal equivalent of 46. Next take each bit of the byte and shift them over one place to the left, filling in the now vacant bit 0 with the padded value 0 as shown below. Bit 7 has nowhere to go since it has no bit 8 position to occupy. The newly vacated bit 0 position is filled with a binary zero.

By shifting all the bits to the left the original number has been *multiplied by two* since the bit 0 value of  $2^0$  has been moved to the  $2^1$  position, bit 1's value of  $2^1$  has been moved to  $2^2$ , etc.

**Note that if the original bit 7 had a value of 1 then it would have been lost giving an incorrect result. This is a condition that *must* be checked for by the programmer and this will be covered in a later section.**

*Division by two* is accomplished by shifting the bit values to the right.

Figure 1-3 Using shift operations to multiply and divide by two

bit 0 → bit 1 → bit 2 → bit 3 → bit 4 → bit 5 → bit 6 → bit 7 → bit 0, ...

For simplicity the registers shown are byte-wide. In reality the width is more often 32 or 64 bits.

Other rotates are possible where the shifted-out bit feeds back to the input, giving a circular action.

Bit0 → Bit1 → Bit2 → Bit3 → Bit4 → Bit5 → Bit6 → Bit7 → Bit0 → Bit1...

**1.3.13. Binary Coded Decimal (BCD)**

Binary Coded Decimal represents decimal numbers in groups of bits, the encoding is normally done in four-bit nibbles. Each bit represents a power of two weight ( $2^3, 2^2, 2^1, 2^0$ , or 8,4,2,1). Since four bits can represent 16 distinct numbers, and there are only ten decimal digits, wastage occurs with this method. An alternative known as *packed BCD* may be used but is less common.

**1.3.13.1. Converting Binary Coded Decimal to Decimal**

BCD is similar to hexadecimal except that hex characters a through f are illegal. A binary grouping of BCD characters could look like:

1001 0111 1000. Each group of 4 bits (nibbles) are read off as follows –

- $1001 = 9$

- $0111 = 7$

- $1000 = 8$

This corresponds to the decimal number 978.

### 1.3.13.2. BCD addition

Adding is straightforward, however if the addition of two nibbles results in a value greater than 9 (1010, 1011, 1100, 1101, 1110, 1111) then it is an invalid decimal number. The resolution is to add 6 (0110) which will bring it back to a valid number. The carry will be added to the next nibble.

Addition examples –

1.

$$14 + 22 = 36 = 0011\ 0110$$

Verify by binary addition

$$0001\ 0100 \text{ (14)}$$

$$0010\ 0010 \text{ (22)} +$$

$$0011\ 0110 \text{ (36)}$$

2.

$$20 + 20 = 40 = 0100\ 0000$$

$$0010\ 0000 \text{ (20)}$$

$$0010\ 0000 \text{ (20)} +$$

$$0100\ 0000 \text{ (40)}$$

3.

$$26+25 = 51 = 0101\ 0001$$

$$0010\ 0110 \text{ (26)}$$

$$0010\ 0101 \text{ (25)} +$$

**0100 1011** Least significant nibble is greater than 9 so add 6

$$0000\ 0110 + (6)$$

$$01010001 \text{ (51)}$$

4.

$121 + 157 = 278 = 0010\ 0111\ 1000$

$0001\ 0010\ 0001$  (121)

$0001\ 0101\ 0111$  (157)+

$0010\ 0111\ 1000$  (278)

5.

$199 + 933 = 1132 = 0001\ 0001\ 0011\ 0010$

$0001\ 1001\ 1001$  (199)

$1001\ 0011\ 0011$  (933)+

**1010 1100 1100** (Two nibbles invalid add 0110 0110

$0000\ 0110\ 0110$  +

**1011 0011 0010** Now, the most significant nibble is invalid so add 6 to it

$0110\ 0000\ 0000$  +

**0001 0001 0011 0010** (1132) Brings in a fourth nibble!

#### 1.3.13.3. Conversion from Hex/Pure Binary to BCD

One way of converting a hex number to BCD is to convert the hex number to decimal and then to BCD. An alternative is to use the double-dabble method.

#### 1.3.13.4. Double-Dabble

The double-dabble algorithm is fairly simple to implement; it consists of a series of shift<sup>11</sup> operations and additions.

**Note that an n digit hex number can translate into more than n decimal digits, (8516 = 13310, FFF16 = 409510).**

The method sets up a store to hold n binary digits and partitions to hold the decimal powers of two – units, tens, hundreds, thousands, ... The partitions are cleared to hold all zeros and then the binary digits are shifted in one bit at a time, adjustments (addition of decimal 3) are made to the partition values dependent on their magnitude (>4). Once all bits have been shifted<sup>12</sup> the algorithm has been completed.

An example:

<sup>11</sup> Shift/Rotate operations are discussed on page 1-13.

<sup>12</sup> The number of shifts is equal to the number of binary digits

Consider the binary number  $00011011$  = hex  $1B$  = decimal 27. The steps to convert from pure binary to BCD are shown in Table 1-6.

Table 1-6 Double-Dabble example

| Hundreds Partition | Tens Partition | Units Partition | Binary Store | Action                                          |

|--------------------|----------------|-----------------|--------------|-------------------------------------------------|

| 0000               | 0000           | 0000            | 00011011     |                                                 |

| 0000               | 0000           | 0000            | 00110110     | Shift left-most bit over to partitions (shift1) |

| 0000               | 0000           | 0000            | 01101100     | Shift left-most bit over to partitions (shift2) |

| 0000               | 0000           | 0000            | 11011000     | Shift left-most bit over to partitions (shift3) |

| 0000               | 0000           | 0001            | 10110000     | Shift left-most bit over to partitions (shift4) |

| 0000               | 0000           | 0011            | 01100000     | Shift left-most bit over to partitions (shift5) |

| 0000               | 0000           | 0110            | 11000000     | Shift left-most bit over to partitions (shift6) |

| 0000               | 0000           | 1001            | 11000000     | Add 3 to units, since unit is 5 or greater      |

| 0000               | 0001           | 0011            | 10000000     | Shift left-most bit over to partitions (shift7) |

| 0000               | 0010           | 0111            | 00000000     | Shift left-most bit over to partitions (shift8) |

Reading off the tens and unit columns gives the value  $27_{10}$ .

**Note 3 is added rather than 6 since the shift left operation multiplies by two!**

A more complex 12-bit example is shown in Table 1-7.

Table 1-7 Three digit double dabble example

## Double Dabble Three digit Hex (200) number

12 binary digits so 12 shifts are required

| Hundreds | Tens    | Units   |         | Binary  |         |                |

|----------|---------|---------|---------|---------|---------|----------------|

| 0 0 0 0  | 0 0 0 0 | 0 0 0 0 | 0 0 1 0 | 0 0 0 0 | 0 0 0 0 | Initial State  |

| 0 0 0 0  | 0 0 0 0 | 0 0 0 0 | 0 1 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #1       |

| 0 0 0 0  | 0 0 0 0 | 0 0 0 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #2       |

| 0 0 0 0  | 0 0 0 0 | 0 0 0 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #3       |

| 0 0 0 0  | 0 0 0 0 | 0 0 1 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #4       |

| 0 0 0 0  | 0 0 0 0 | 0 1 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #5       |

| 0 0 0 0  | 0 0 0 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #6       |

| 0 0 0 0  | 0 0 0 0 | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Add 3 to units |

| 0 0 0 0  | 0 0 0 0 | 1 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #7       |

| 0 0 0 0  | 0 0 0 0 | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Add 3 to units |

| 0 0 0 0  | 0 0 0 1 | 0 1 1 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #8       |

| 0 0 0 0  | 0 0 0 0 | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #9       |

| 0 0 0 0  | 0 0 0 1 | 1 0 0 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Add 3 to tens  |

| 0 0 0 0  | 0 0 1 1 | 0 0 1 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #10      |

| 0 0 0 0  | 1 0 0 1 | 0 1 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Add 3 to units |

| 0 0 0 1  | 0 0 1 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #11      |

| 0 0 0 0  | 0 0 0 0 | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Add 3 to Tens  |

| 0 0 0 1  | 0 0 1 0 | 1 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | Shift #12      |

| 0 0 1 0  | 1 1 0 1 | 0 1 1 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 |                |

| 0 0 0 0  | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 |                |

| 0 0 1 0  | 1 0 0 0 | 0 1 1 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 |                |

| 0 0 0 0  | 0 0 0 0 | 0 0 1 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 |                |

| 0 0 1 0  | 1 0 0 0 | 1 0 0 1 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 |                |

| 0 1 0 1  | 0 0 0 1 | 0 0 1 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 |                |

5

1

2

200 hex = 001000000000 binary = 512 decimal

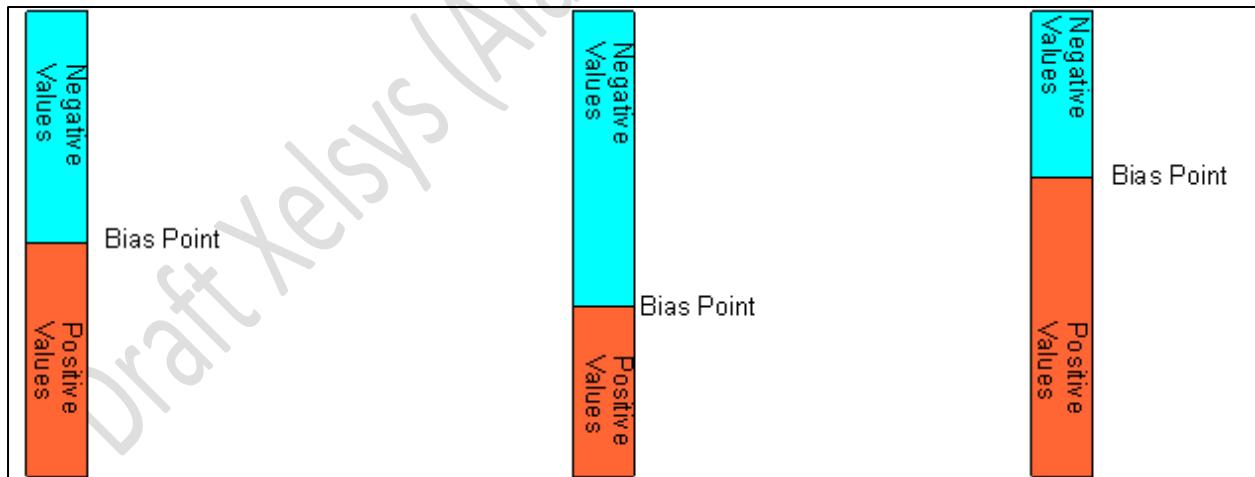

## 1.3.14. Floating Point

An integer is a whole, complete and exact number such as 107 or 456. There is a limit to magnitude within a simple unit of storage such as a register. With floating-point representation a range of extremely large or extremely small numbers can be represented at the expense of precision. This means that a floating-point number may be an approximation that introduces *rounding* to nearest digits. There are two main parts to a floating-point number, the *significand* or *mantissa* and the *exponent*. There is also provision for a sign bit. The form is *significand* multiplied by the *base* raised to a *power*, an example being  $3,450,000 = 345 \times 10^4$ . Here 345 is the significand, ten is the base and four is the exponent.

There is a standard *IEEE 754* (<https://standards.ieee.org/ieee/754/6210/>) which is a specification for floating-point arithmetic. The standard defines Single and Double floating-point formats<sup>13</sup> as shown in Table 1-8. There is also provision to include Not-a-Number<sup>14</sup> (NaNs) and  $\pm\infty$ .

A 32-bit single precision floating-point binary number within IEEE 754 is defined as:

|                         |                          |                              |