THE REPORT

# TC1775B

Understanding the BootStrap Loaders

TC1775B

Microcontrollers

Never stop thinking.

#### TC1775B

|  |  | 2002-09                             | V 1.1 |  |

|--|--|-------------------------------------|-------|--|

|  |  | 2001-06                             | V 1.0 |  |

|  |  | (major changes since last revision) |       |  |

|  |  | to Infineon Template                |       |  |

|  |  |                                     |       |  |

|  |  |                                     |       |  |

|  |  |                                     |       |  |

|  |  |                                     |       |  |

Controller Area Network (CAN): License of Robert Bosch GmbH

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

Edition 2002-09

Published by

Infineon Technologies AG

81726 München, Germany

© Infineon Technologies AG 2006.

All Rights Reserved.

#### **LEGAL DISCLAIMER**

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# AP32034 TC1775B BootStrap Loaders

| Table of                                                         | Contents                                                                                                                                                                                                                                                                        | Page                                   |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1                                                                | Introduction                                                                                                                                                                                                                                                                    | 4                                      |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.6.1             | Common BSL Configuration Booting Scheme Hardware Booting Scheme Entering the Bootstrap Loader Mode Interrupts Internal Register settings TC1775B Operating Frequency PLL Factors                                                                                                | 5<br>5<br>6<br>6                       |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                           | ASC The ASC Bootstrap Loader Initialization Entering the ASC Bootstrap Loader Exiting the ASC Bootstrap Loader ASC Boot Algorithm for the Internal ROM Program Flow ASC Timing                                                                                                  | 8<br>9<br>9<br>11                      |

| 4<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7               | SSC The Synchronous Serial Channel (SSC) Bootstrap Loader Initialization Entering the SSC Bootstrap Loader Loading the Startup Code Baud rate generation for the BSL Exiting the SSC Bootstrap Loader SSC Boot Algorithm SSC BSL Data Transfer Timing                           | 14<br>15<br>15<br>15<br>18<br>19       |

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | CAN The CAN Bootstrap Loader TC1775B Operating Frequency Initialization Measurement of dominant CAN bits Requirements of the Host Message Detection using the Analyzing mode Loading the Code Exiting the Bootstrap Loader Mode Choosing the Baud rate for the Bootstrap Loader | 24<br>24<br>25<br>25<br>26<br>26<br>27 |

| 5.10<br>5.11                                                     | TwinCAN Boot Algorithm                                                                                                                                                                                                                                                          |                                        |

# AP32034 TC1775B BootStrap Loaders

Introduction

## 1 Introduction

This document describes the functionality of the BootStrap Loaders (BSL) that are available for the TC1775B Infineon's 32-Bit Microcontroller. There are presently three different modes of operation available for the BSL. An asynchronous serial channel (ASC) which has similar functionality as to the BSL that is found on Infineon's 16-bit (C16x) family of microcontrollers. The two additional serial BSL's that have been added are an Synchronous Serial Channel (SSC) and a Controller Area Network (CAN).

# AP32034 TC1775B BootStrap Loaders

Common BSL Configuration

# 2 Common BSL Configuration

The section describes the common features of all of the bootstrap loaders.

## 2.1 Booting Scheme

The bootstrap loader is an integrated mechanism that can be selected via a port configuration during a system start after reset. If the bootstrap loader mode is selected during reset, program execution is started from the Internal Boot ROM.

## 2.2 Hardware Booting Scheme

The hardware booting scheme uses the state of a number of external pins, sampled and latched with a power-on-reset, to determine the start configuration of the chip. The state of these pins is latched into the Reset Status Register (RST\_SR) when the power-on-reset signal (pin PORST) is released and transitions to a high level (while PORST is active the latches are transparent). The hardware configuration is determined by the value of bits OCDS\_E, BRK\_IN and CFG[3:0]. The latched values can only be changed by another power-on-reset and are used for all hardware-invoked reset options (power-on, hard, watchdog and wake-up reset). Table 1 shows the Available BootStrap Loaders (BSL) options available in the TC1775B.

Table 1 Available Bootstrap Loader ROM Selection

| OCDSE | BRKIN | CFG[3:0]          | Type of Boot         | <b>Boot Source</b> | PC Start<br>Value      |

|-------|-------|-------------------|----------------------|--------------------|------------------------|

| 1     | 1     | X000 <sub>B</sub> | ASC Bootstrap Loader | Boot ROM           | BFFF FFFC <sub>H</sub> |

| 1     | 1     | X001 <sub>B</sub> | SSC Bootstrap Loader | Boot ROM           | BFFF FFFC <sub>H</sub> |

| 1     | 1     | X010 <sub>B</sub> | CAN Bootstrap Loader | Boot ROM           | BFFF FFFC <sub>H</sub> |

## 2.3 Entering the Bootstrap Loader Mode

If the selection matches the configuration for the bootstrap loader as shown in **Table 1**. Then program execution begins in the internal 8 KByte boot ROM memory (BFFF FFFF<sub>H</sub> - BFFF E000<sub>H</sub>). The particular BSL routine that runs is determined by the main boot software reading the value of the CFG[3:0] bits and jumping to the respective routine.

## AP32034 TC1775B BootStrap Loaders

#### **Common BSL Configuration**

#### 2.4 Interrupts

The bootstrap loader software is very simplistic and does not use interrupts. The user should take this into account when attempting to use very high baud rates when connecting to the serial ports.

Note: The user should locate their code assuming a start address of C000 0004<sub>H</sub>.

## 2.5 Internal Register settings

When the TC1775 has entered BSL mode, the following configuration is automatically set.

Table 2 CPU Register Settings

| Watchdog Timer     | Disabled | BIV  | TBD |

|--------------------|----------|------|-----|

| ENDINIT Protection | Enabled  | BTV  | TBD |

| SYSCON             | TBD      | ISP  | TBD |

| ICR                | TBD      | PCXI | TBD |

| LCX                | TBD      | FCX  | TBD |

All other registers TBD.

Note: The main bootstrap loader routine has configured TBD CSA's.

# 2.6 TC1775B Operating Frequency

The user must be aware that the TC1775B has no way of determining at what frequency it is operating at. Therefore, the user must have some system knowledge and understanding of the possible communication baud rates can be generated by the TC1775B.

The ASC0, SSC0, and TwinCAN modules are all clocked at the same frequency as the  $f_{SystenClk}$  and assume the base crystal frequency is 16 MHz.

#### 2.6.1 PLL Factors

The following equation defines the relationship between the  $f_{OSC}$  and  $f_{SystenClk}$ . The PPL "N" factor is controlled via the dedicated pins CLKSEL[2:0], while the PLL "K" factor is controlled via the PLLDIVCLK (on reset K factor = 10) field in register PLLCLC.

[1]

$$f_{SystemClk} = \frac{\left(N \cdot f_{OSC}\right)}{K}$$

# AP32034 TC1775B BootStrap Loaders

# **Common BSL Configuration**

An example of a typical clock configuration setting would be as follows:

Table 3 Clock Parameters

| CLKSEL[2:0]      | 010 <sub>B</sub> | Selects a "N" factor equal to 10                                              |

|------------------|------------------|-------------------------------------------------------------------------------|

| PLLDIVCLK        | 111 <sub>B</sub> | Unchanged from Reset value, "K" factor is equal to 10                         |

| BYPASS           | O <sub>B</sub>   | is at a logic level low, i.e. $f_{\text{SystemClk}}$ is supplied from the PLL |

| f <sub>OSC</sub> | 16 MHz           | Base Crystal Frequency                                                        |

This results in a f<sub>SystemClk</sub> of 16 Mhz.

Note: For more information regarding the clock settings please refer to the TC1775B Users Manual.

**ASC**

## 3 ASC

## 3.1 The ASC Bootstrap Loader

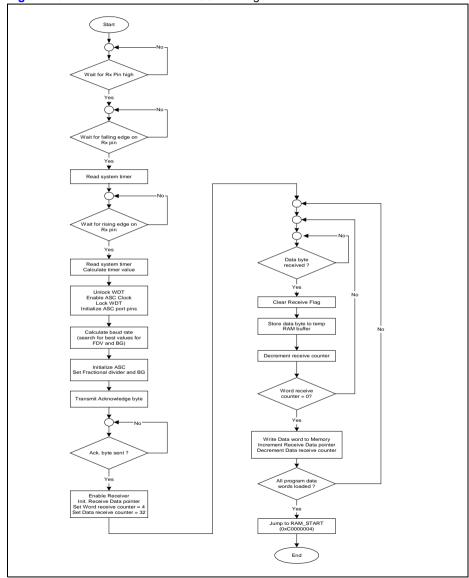

The built-in ASC bootstrap loader of the TC1775B provides a mechanism to load the startup program, which is executed after reset, via the asynchronous serial interface. In this case no external (ROM) memory is required for the initialization code. The bootstrap loader moves 128 bytes of code/ data into the internal SPRAM starting at address C000  $0004_{\rm H}$ .

Most probably the initially loaded routine will load additional code or data. This second receive loop may directly use the pre-initialized ASC interface to receive data and store it to arbitrary user-defined locations.

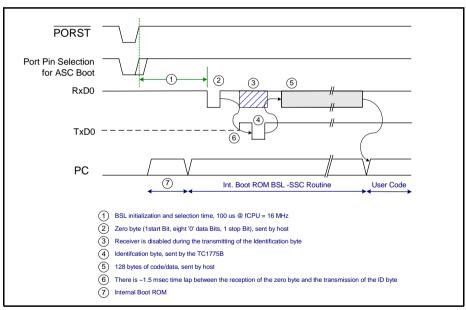

Figure 1 ASC Bootstrap Loader Sequence

Application Note 8 V 1.1, 2002-09

**ASC**

#### 3.2 Initialization

The ASC BSL initializes the ASC0 in the following way:

- Receive data pointer is initialized to address C000 0004<sub>H</sub>

- baud rate depends on host (auto baud rate detection)

- 8 data bits

- · one start/stop bit

- · ASC0 interface is selected via port pins

- P12.12RxD0

- P12.13TxD0

## 3.3 Entering the ASC Bootstrap Loader

The ASC bootstrap loader code is a routine contained within the boot ROM of the TC1775B. TC1775B enters SSC BSL mode when the pin configuration shown in **Table 4**

Table 4 ASC Bootstrap ROM Selection

| OCDSE | BRKIN | CFG [3:0]         | Type of Boot            | <b>Boot Source</b> | PC Start Value         |

|-------|-------|-------------------|-------------------------|--------------------|------------------------|

| 1     | 1     | X000 <sub>B</sub> | ASC Bootstrap<br>Loader | Boot ROM           | BFFF FFFC <sub>H</sub> |

The first task ASC0 needs to perform is to determine the baud rate at which the host is communicating at. This is done by capturing the time period of a zero byte (one start bit and eight "0" data bits) transmitted by the host and received at the ASC0 receive pin. Therefore, a software polling loop begins by first waiting for the ASC0 receive pin to remain at a high level. Once a high level has been detected the software now begins looking for a falling edge. After a falling edge has been detected the system timer is read and the software now looks for a rising edge.

When the rising edge is found the system timer is read again and the difference between the two readings is calculated. This value represents the time period for one zero byte transmitted by the host and is the basis for calculating the host baud rate with respect to the f<sub>SYSCLK</sub> clock.

The next step is to enable the ASC clock generator. This requires a password unlock sequence to be performed to the WDT to gain write access to the ASC CLC Control register ( $f_{SYSCLK} = f_{ASC}$ ). After writing the ASC CLC register the WDT is then locked again.

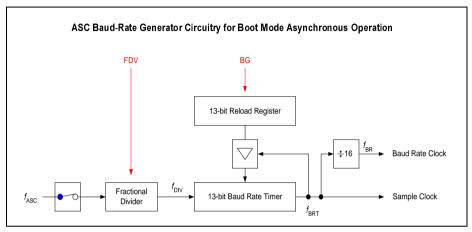

The ASC boot loader continues by initializing the serial port pins and calculating the baud rate. The baud rate is calculated by searching for the best values for the Fraction Divide Value (FDV) and Baud rate Generator (BG) registers.

Figure 2, represents the block diagram of the ASC Baud Rate Generator.

Figure 2 ASC Baud Rate Generator

The software must now determine the values to be written in the Fractional Divide Value register and the Baud rate Generator register. The Baud rate is found by using min/max boundaries to find the best fit value for BG as shown in the following formulas.

*Timer Value* = Measured system timer tick for a zero byte transmission

$$baud\_rate_{{\scriptscriptstyle ASC}} = \frac{9 \cdot f_{{\scriptscriptstyle ASC}}}{TimerValue}$$

$$baud\_rate_{ASC} = \frac{FDV}{512} \cdot \frac{f_{ASC}}{16 \cdot (BG + 1)}$$

Therefore substituting for baud\_bate\_ASC in the equations and solving for BG:

$$\frac{9}{TimerValue} = \frac{FDV}{(512 \cdot 16 \cdot (BG + 1))}$$

Application Note 10 V 1.1, 2002-09

**ASC**

$$\frac{9 \cdot 512 \cdot 16}{TimerValue} = \frac{FDV}{BG + 1}$$

$$FDV = \frac{73728 \cdot BG}{TimerValue} + \frac{73728}{TimerValue}$$

$$\frac{73728 \cdot BG}{TimerValue} = FDV - \frac{73728}{TimerValue}$$

$$73728 \cdot BG = FDV \cdot TimerValue - 73728$$

$$BG = \frac{FDV \cdot TimerValue}{73728} - 1$$

Next the ASC0 is initialized (receive pin remains disabled) to the baud rate of the host, an identification byte ( $D5_H$ ) is returned to the host indicating the device is ready to accept a data transfer from the host of **exactly 128 bytes**. The ASC0 receive pin is enabled after the identification byte has been transmitted.

The software now enters two receive loops. The inner loop is waiting until it has received four bytes. The outer loop will write (word) the word access to the program memory. This process repeats until 128 bytes have been received.

Note: The ASC bootstrap loader expects a block size of exactly 128 bytes (32 words).

# 3.4 Exiting the ASC Bootstrap Loader

Once 128 bytes have been received and written to program memory a "Jump Indirect" command (JI) is performed to the memory location C000 0004<sub>H</sub> and program execution begins at this point (user program).

# 3.5 ASC Boot Algorithm for the Internal ROM Program Flow

Figure 3 shows a flowchart of the ASC boot algorithm.

Figure 3 ASC Boot Algorithm

## 3.6 ASC Timing

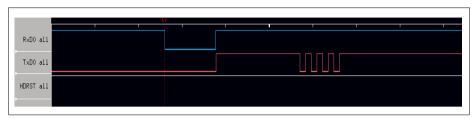

Figure 4 Logic Analyzer Trace of the actual data transfer

#### Typical Timing (Bus Clock 16 KHz, 9600 Baud)

Boot Initialization (Host must wait before sending the zero byte from the rising edge of PORST)

~ 100 usec

From rising edge of RxD (host last data bit) to the falling edge of TxD (Start bit from the TC1775 sending the ID byte).

~ 1.5 msec

Delay from the reception of the ID byte to the host downloading data

~ 100 usec

Between byte transfers

~at high baud rate the user may need to add inter-byte delays

## 4.1 The Synchronous Serial Channel (SSC) Bootstrap Loader

The built-in Synchronous Serial Channel bootstrap loader of the TC1775B provides a mechanism to load a user defined program via the SSC0 interface. The bootstrap loader moves code/data into the internal Scratch Pad RAM (SPRAM) starting at location "C000 0004<sub>H</sub>".

The default SSC BSL configuration is assumed to have an SPI compatible EEPROM (25xxx series) connected to the TC1775B's SSC0 port. The SSC BSL supports memory devices with 8-bit or 16-bit addressing and any other possibility can be assumed by the user if they understand this default configuration.

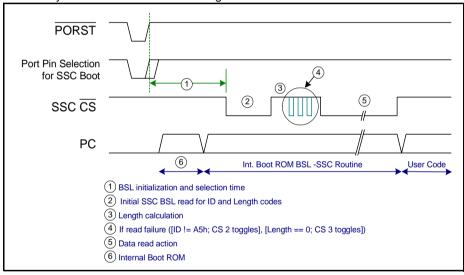

Figure 5 SSC Bootstrap Loader Sequence

#### 4.2 Initialization

The SSC BSL initializes the SSC0 in the following way:

- · CPU is master for master mode

- SPI mode 0 (0,0)

- 1 MHz clock rate (16 MHz external clock)

- · Data length 8-Bits

- Port pin assignment (4 Pins)

- Receive data pointer set to address C000 0004<sub>H</sub>

- · SPI memory chip-select via port pin

- P13.6SCLK

- P13.7MRST

- P13.8MTSR

- P11.14 CS

## 4.3 Entering the SSC Bootstrap Loader

The SSC bootstrap loader code is stored in and is part of the TC1775B boot ROM. The TC1775B enters SSC BSL mode when the pin configuration shown in **Table 5** following a PORST.

Table 5 SSC Bootstrap ROM Selection

| OCDSE | BRKIN | CFG [3:0]         | Type of Boot            | <b>Boot Source</b> | PC Start Value         |

|-------|-------|-------------------|-------------------------|--------------------|------------------------|

| 1     | 1     | X001 <sub>B</sub> | SSC Bootstrap<br>Loader | Boot ROM           | BFFF FFFC <sub>H</sub> |

# 4.4 Loading the Startup Code

The port pins for the SSC0 and  $\overline{\text{CS}}$  are setup along with the SSC operating parameters. The boot software attempts to set the SSC clock frequency to a nominal rate of 1 MHz (assuming a base crystal frequency of 16 MHz) where the actual baud rates shown in Table 6

Table 6 Actual SSC Baud Rates using 16 MHz Basic Clock (K<sub>factor</sub> = 7)

| CLKSEL[2:0] | N Factor | $f_{\text{OSC}} = f_{\text{SSC}} \text{ (MHz)}$ | BR <sup>1)</sup> | Actual Baud Rate (MHz) |

|-------------|----------|-------------------------------------------------|------------------|------------------------|

| 000         | 8        | 12.80                                           | 5                | 1.067                  |

| 001         | 9        | 14.40                                           | 6                | 1.029                  |

| 010         | 10       | 16.00                                           | 7                | 1.000                  |

| 011         | 11       | 17.60                                           | 7                | 1.100                  |

| 100         | 12       | 19.20                                           | 8                | 1.067                  |

Table 6 Actual SSC Baud Rates using 16 MHz Basic Clock (K<sub>factor</sub> = 7)

| CLKSEL[2:0] | N Factor | $f_{\rm OSC} = f_{\rm SSC}$ (MHz) | BR <sup>1)</sup> | Actual Baud Rate (MHz) |

|-------------|----------|-----------------------------------|------------------|------------------------|

| 101         | 13       | 20.80                             | 9                | 1.040                  |

| 110         | 14       | 22.40                             | 10               | 1.018                  |

| 111         | 15       | 24.00                             | 11               | 1.000                  |

<sup>1)</sup> BR is rounded down in the calcuation

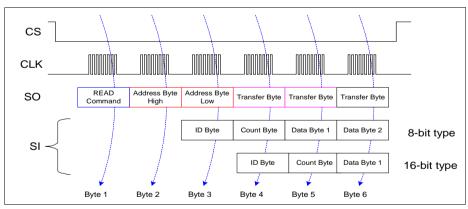

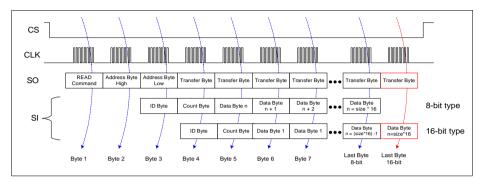

The SSC BSL will basically perform two read accesses (see Figure 7 and Figure 8). The first read access is to determine the addressing mode and the number of bytes to read. The second access is to actually load the user program into its internal program RAM. There is also the possibility of detecting two data format errors. The errors are either for an incorrect Identification byte or zero data length. The user is notified of an error on the  $\overline{\text{CS}}$  line. The toggling of the  $\overline{\text{CS}}$  line between the two read access would indicate that an error occurred during the initial read access.

Both read access begin by the SSC sending a read command (data value = 3) with a memory start address of zero. The SSC BSL determines the type of memory (8- or /16-bit addressing) by checking at which position the memory identifier byte is located. An example of the memory map of an EEPROM device is shown in **Table 7**. For memory types with 8-bit addressing this will happen after the first address byte, for memory types with 16-bit addressing this happens after the second address byte is read. If the correct memory identifier byte is not equal to  $5A_{\rm H}$  then the CS line is quickly toggled twice and then the software enters an endless loop. Assuming there was not an error the data byte following the memory identifier is assumed to be the size index byte. The size index informs the bootstrap loader of the number of bytes multiplies by 16 that are to be received. This allows block of up to 2040 (32-bit) or 4080 (16-bit) instructions can be loaded into memory. This process continues until all bytes have been read from the serial memory.

Table 7 Content of the EEPROM

| <b>EEPROM Address</b> | Data value | Meaning                                   |

|-----------------------|------------|-------------------------------------------|

| 0x0000                | 0x5A       | Memory Identifier (ID)                    |

| 0x0001                | 0x010xFF   | Size Index (Number of bytes to load * 16) |

| 0x00020x1FE2          | 0x000xFF   | User Code/Data                            |

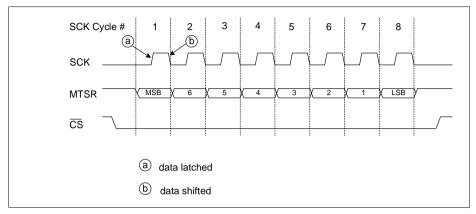

Figure 6 Example of SPI Mode 0

Note: The SSC BSL uses mode 0 to communicate thereby bit PH is set to "1" and bit PO is set to "0" in register SSCx\_CON.

Figure 7 Initial SSC BSL data transfer

Figure 8 Second SSC BSL data transfer

## 4.5 Baud rate generation for the BSL

The BSL has no way to determine its base clock frequency and therefore assumes that this is 16 MHz. Additionally, the K factor of the PLL is not modified by the BSL so it remains at its default value of seven. The BSL will automatically enable the SSC clock and the set the value of the SSC Clock divider to 1 (unity) so that the SSC clock frequency is equal to the system clock frequency f<sub>SYSCLK</sub>. The system clock frequency for TC1775B is determined from the following formula:

$$f_{SYSCLK} = \frac{N}{K} \cdot f_{OSC}$$

The calculation of the reload value is done by:

$$< BR > = \left(\frac{f_{SSC}}{2 \cdot baud\_rate_{SSC}}\right) - 1$$

The actual baud\_rate\_SSC value must be determined from the following formula:

$$baud\_rate_{SSC} = \frac{f_{SSC}}{2 \cdot (\langle BR \rangle + 1)}$$

## AP32034 TC1775B BootStrap Loaders

SSC

## 4.6 Exiting the SSC Bootstrap Loader

Once all bytes (size index \* 16) have been read and written to program memory a "Jump Indirect" command (JI) is performed to the memory location C000 0004<sub>H</sub> and program execution begins at this point (user program).

Note: The user should locate their program to a start address of C000 0004<sub>H</sub>.

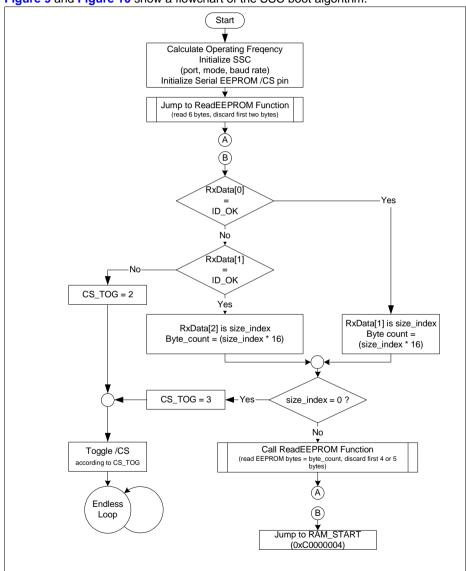

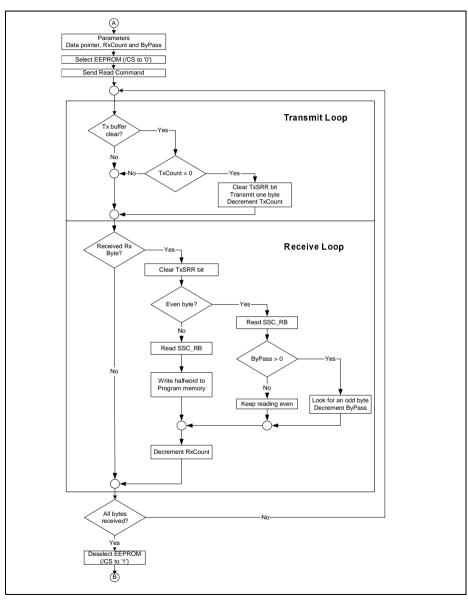

## 4.7 SSC Boot Algorithm

Figure 9 and Figure 10 show a flowchart of the SSC boot algorithm.

Figure 9 SSC Boot Algorithm (Sheet 1/2)

Figure 10 SSC Boot Algorithm (Sheet 2/2)

Figure 11 Logic Trace of the start of the SSC BSL data sequence.

## Typical SSC BSL Timing (Bus Clock 16 KHz)

Boot Initialization (rising edge of HDRST and the falling edge of CS)

~ 60 usec

From rising edge CS to the first rising edge of SCLK.

~ 15 usec

Delay between byte transfers

~ 12 usec

Time from the falling edge of the last SCLK and the rising edge of CS.

~ 4 usec

CS high time between the first and second read assesses.

~ 3 usec

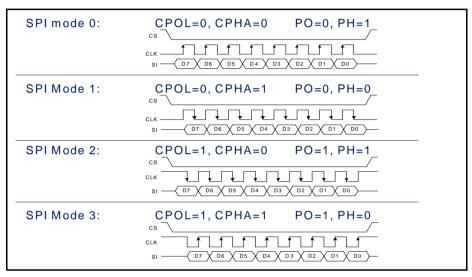

#### **SPI Mode Definitions:**

Clock Polarity is defined by symbols CPOL and PO.

Clock Phase is defined by symbols **CPHA** and **PH**. Please note that Infineon defines the value of the clock phase to be inverted to the normally accepted industry standard (see **Figure 12**).

Figure 12 Industry accepted SPI transfer modes and settings compared to Infineon's definition

## 5 CAN

## 5.1 The CAN Bootstrap Loader

The built-in CAN bootstrap loader of the TC1775 provides a mechanism to load a program via the TwinCAN module (port pins P13[12:13]). The bootstrap loader is an integrated mechanism that can be selected via a port configuration during a system start after reset. If the bootstrap loader mode is selected during reset, program execution is started from the Internal Boot ROM. The bootstrap loader program will configure its CAN module to the baud rate of the Host in order for communications to transpire. Once communication has been established, the bootstrap loader receives a Host defined variable number of messages for downloading of the code/data. The received code/data is sequentially written to the on-board Local Code Scratch Pad RAM (SPRAM). In the TC1775, there are 32 Kbytes of SPRAM available for program execution. After the download has been completed, the program execution continues by jumping to the start of the SPRAM (C000 0004<sub>H</sub>).

The bootstrap loader mechanism may be used for standard system startup as well as for special occasions like system maintenance (firmware update), end-of-line programming or testing.

## 5.2 TC1775B Operating Frequency

The user must be aware that the TC1775B has no way of determining at what frequency it is operating at. Therefore, the user must have some system knowledge and understanding of what CAN baud rates can be detected from the Host.

A PC based software executable is provided which determines what baud rates the TC1775B is capable of receiving based on its system clock frequency ( $f_{\text{SystemClk}}$ ).

#### 5.3 Initialization

The CAN BSL initializes the TwinCAN in the following way:

- The CAN module 0 is used but not initialized until a message is detected

- Message Object 0 is configured to receive a standard CAN frame with a message identifier of 555<sub>H</sub>.

- Receive data pointer set to address C000 0004<sub>H</sub>

- CAN port pins

- P13.12RxCAN0

- P13.13TxCAN0

Note: It is recommend that Port13 have no floating inputs or any of its pins changing states other than P13.12. The CAN BSL software determines the bit timing by reading the entire port and using it for sampling time calculations.

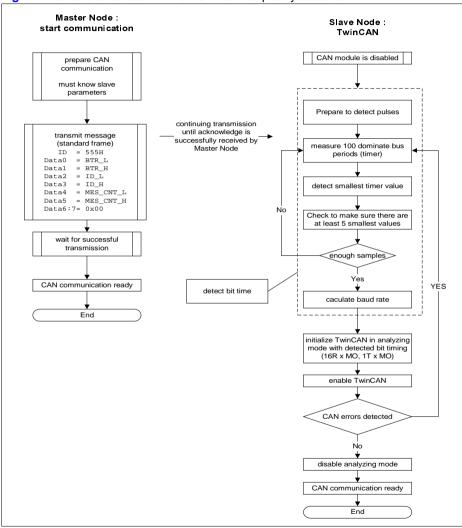

#### 5.4 Measurement of dominant CAN bits

The System Timer is used for the measurement of a dominant bit on the CAN bus. The System Timer is running at the same frequency as the CPU and thus supports the highest possible resolution.

During this time the CAN module is disabled and the TC1775B software is polling the RXDC0 (P13.12) pin to detect pulse bus periods (capturing the time between any edge). This process will continue until 100 pulses have been measured. Then, a software algorithm will analyze the data to determine the smallest pulse. From this, the data is further analyzed to obtain an average of the smallest pulses. This time period is assumed to be one CAN bit time and, therefore, it is used for the initial setting for detecting the correct baud rate.

## 5.5 Requirements of the Host

The host will initiate communication with the TC1775B by transmitting a standard CAN message (11-bit Identifier). However, for the TC1775B to properly determine the message baud rate, certain restrictions are imposed on the Host.

- There is a Point-to-Point connection between the Host and TC1775B

- The sample point of a CAN bit is at 80%

- A baud rate is used which the TC1775B is capable of detecting

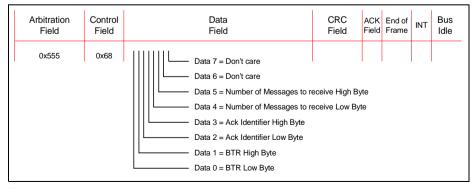

- The first message the Host sends is of the format below

- The identifier for the standard message is 555<sub>H</sub>

- The data length code is set to 6

- Data bytes 0 and 1 are the values for the TC1775B's Bit Timing Register (BTR)

- Data bytes 2 and 3 contain the identifier for an acknowledge message that the TC1775B sends back to the Host.

- Data bytes 4 and 5 make up the 16-bit value for the number of messages to receive

Figure 13 Format of the first message transmitted by the Master

Application Note 25 V 1.1. 2002-09

## AP32034 TC1775B BootStrap Loaders

CAN

The Host will transmit this message and wait for the TC1775B to acknowledge it. Since there are no other nodes (Point-to-Point) on the bus, the CAN controller of the Host will continually repeat the transmission of the message. This is because the TC1775B has not responded with a dominant bit in the Acknowledge Slot of the transmitted message from the Host. After the first message the Host's CAN error management logic will send error frames until its internal error state changes from error active to error passive. After a short period of time the TC1775B should be able to detect the Host's baud rate and acknowledge the Host's message.

## 5.6 Message Detection using the Analyzing mode

There is a CAN Analyzer Mode available on the TwinCAN which provides the means to monitor CAN bus traffic without participating in the CAN protocol itself. This mode is used in conjunction with the bit measurement to determine non-destructively (without errors) the baud rate at which the Host is transmitting its message. The TC1775B will attempt to recognize the message being broadcast by the Master in analyzer mode. Once the TC1775B can detect the Master's message without errors, the TC1775B will enable its CAN module. The CAN module on the TC1775B will now acknowledge the Master's message. This signals the Master that communication has been established with the TC1775B. If the message cannot be detected within a time-out period, the process will be restarted by recapturing dominant bits and repeating these steps until a message can be found.

# 5.7 Loading the Code

The first message transmitted by the Host contains three variables necessary to load the code/data. Data bytes 0 and 1 contain the information for the TC1775B's Bit Timing Register (BTR). This provides the Host the ability to change these protocol parameters to suit the individual user's needs. However, the user must insure that the correct value is sent; otherwise, communication could be halted. The TC1775B will re-initialize its CAN module to these parameters and transmit a data frame with the identifier (data bytes 2 and 3) sent from the Host.

Data bytes 4 and 5 tells the TC1775B the number of code/data messages to receive. All messages received from this point on will have their data bytes sequentially written into the internal SPRAM starting at location C000 0004<sub>H</sub>. Since data bytes 4 and 5 are defined by the Host, the Host has the ability to decide on how large of a program to load. Therefore, the theoretical maximum number of code/data bytes that can be received is equal to 524,280 (65535 \* 8 code/data bytes). However, the size of the internal SPRAM is 32 Kbytes which results in a maximum of 16,382 16-bit instructions.

Note: The bootstrap loader assumes all message data is valid. The Host should send its code/data sequentially in multiples of 8 code/data bytes. The user is limited to sending a maximum of 2047 messages.

## 5.8 Exiting the Bootstrap Loader Mode

Once all messages have been received, the bootstrap loader will transfer program execution to the user code by jumping to location  $C000\ 0004_H$  (i.e. the first loaded instruction). The Bootstrap Loader sequence is now terminated and the program that was loaded from the Host is now executing.

While in bootstrap loader mode, it is also possible to execute normal user mode. This is because the boot ROM is located in its own memory space.

## 5.9 Choosing the Baud rate for the Bootstrap Loader

When choosing a baud rate, the Master must determine what CAN baud rate is possible for the TC1775B to detect. The major consideration in this determination is the operating frequency of the TC1775B. In general, it is recommended to select the slowest possible baud rate for the initial message with a Sample Point (SP) at 80%. Once communication has been established, the baud rate can be changed to a higher rate.

The bootstrap loader software is polling the CAN receive pin to determine the amount of time that is required for a bit to be transmitted. The higher the ratio of CPU frequency to CAN bit time, the greater the likelihood for early baud rate detection.

Once the bit time has been determined as described in **Section 5.4**, the algorithm for determining the Host baud rate is started. The baud rate is determined by performing an iterative loop using the parameters in **Table 8**, along with equations [3] and [4]. The first objective of the algorithm is to find a solution that uses the maximum number of time quanta ( $N_{tq}$ ). This is done by looping through the three possibilities in **Table 8** to get the calculated timer value result for each possibility. If an exact match between the calculated timer value and the measured timer value is found, then the loop will exit with the current parameters. However, if an exact match is not found, then a search is made to select the closest calculated value to the measured value. The process continues from this point on as described in **Section 5.6**.

Table 8 Time Quanta Parameters for 80% Sample Point

| Item | N <sub>tq</sub> | Tseg1 | Tseg2 | SP    |

|------|-----------------|-------|-------|-------|

| 1    | 20              | 15    | 4     | 80.0% |

| 2    | 15              | 11    | 3     | 80.0% |

| 3    | 10              | 7     | 2     | 80.0% |

# AP32034 TC1775B BootStrap Loaders

CAN

The dependency between the system timer ticks and one CAN bit time (one Time Quantum) is calculated with the following equations:

$$N_{tq}$$

= TimerValue=  $\frac{t_{CANbit}}{f_{SystemClk}}$  [2]

$$BPR = \left(\frac{TimerValue}{N_{tq}}\right) - 1$$

[3]

CalTimerValue =

$$(BPR + 1) \bullet N_{ta}$$

[4]

$$N_{to} = Sync + Tseg1 + Tseg2$$

[5]

#### Where:

BPR Baud rate prescaler value

• TimerValue Number of System Timer ticks

N<sub>tq</sub> Number of time quanta per bit period

t<sub>CANbit</sub> One CAN bit time

Tseg1 Number of time quanta before the sample point

Tseg2 Number of time quanta after the sample point

Sync

Synchronization segment (always equal to 1)

f<sub>SystemClk</sub> CPU operating frequency

From the ISO-DIS 11898 standard, the following assumptions about the bit timing parameters can be made.

$$8 \le t_{\alpha} \le 25$$

$3 \le TSeg1 \le 16$

$2 \le TSeg2 \le 8$

$1 \le SJW \le 4$

The value for SJW is always assumed to be one.

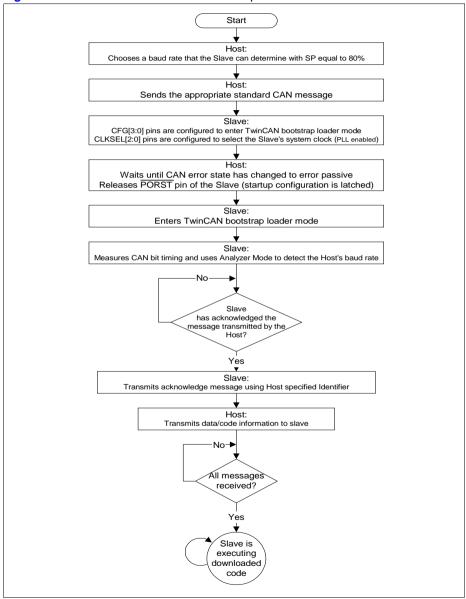

## 5.10 TwinCAN Boot Algorithm

Figure 14 shows a flowchart of the TC1775B frequency detection.

Figure 14 TC1775B Frequency Detection

Figure 15 shows the Host / TC1775B Bootstrap Loader flow.

Figure 15 Host Boot Flow

## 5.11 CAN Plots of Data Sequences

Figure 16 Host message (error active)

Figure 17 Host message (error passive)

Figure 18 TC1775 TwinCAN module acknowledges the host message

Figure 19 TC1775 TwinCAN module transmits response to the host

Figure 20 Overview of the CAN Tx/Rx Sequence

# Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com