# **ELEC3500: Digital Electronics**

## LAB 3: CMOS Combinational Logic

Lab Section: A3 Tuesday 11:30a.m. – 2:30p.m.

Date Performed: October 1st, 2019

Date Submitted: October 2<sup>nd</sup>, 2019

Bomi Garuba - 101082652

Kimberley Nguyen- 101031915

### 1. The MUX

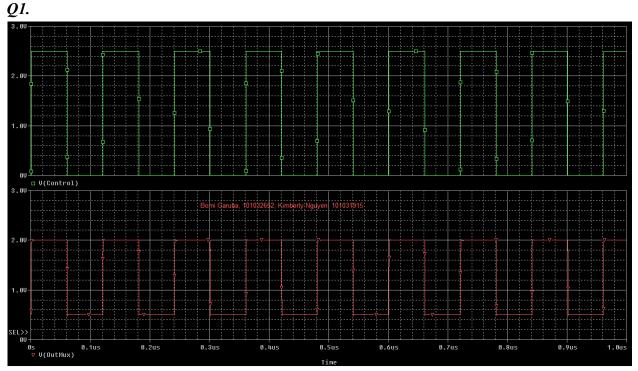

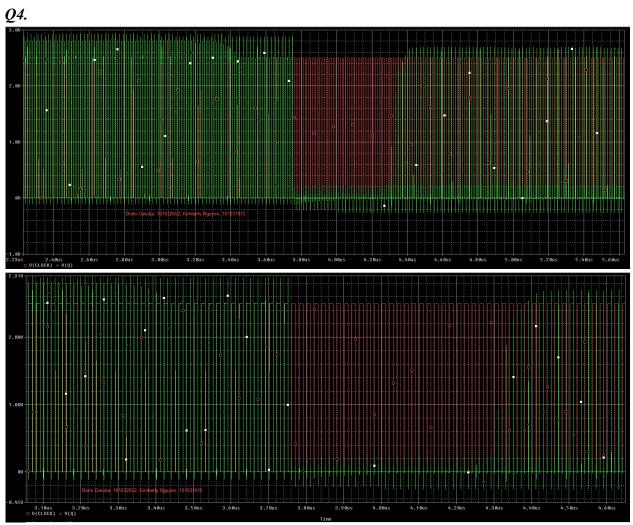

Fig 1. Output waveforms for CTRL and Y signals When the CLK is high, the "d" transmission gate turns ON (why? Because its PMOS component is being fed CLK<sub>inverse</sub> Which is low it turns ON and its NMOS component is getting CLK that which is high). Input thus latches to "d".

When the CLK is low, the "q" transmission gate turns ON (why? Because its PMOS component is being fed CLK Which is low it turns ON and its NMOS component is getting CLK<sub>inverse</sub> that which is high). Input thus latches to "q".

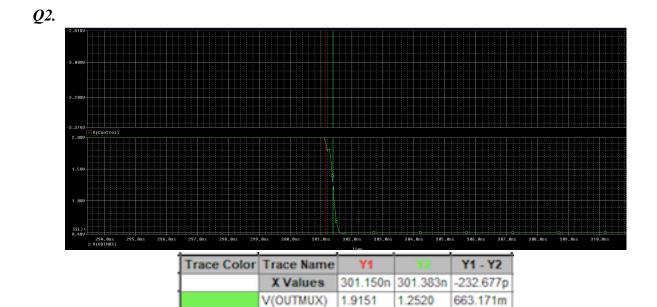

Fig 2. Measuring time from Control High to Y Valid

1.2529

0.000

1.2529

CURSOR 1,2 V(Control)

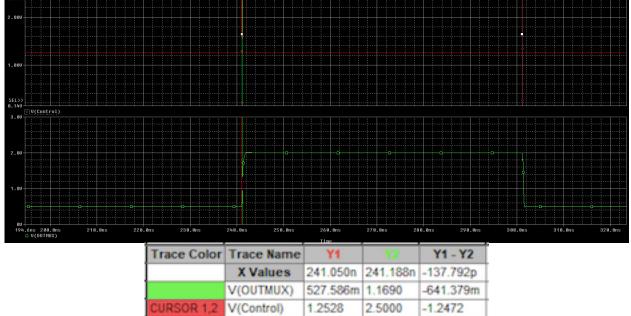

Fig 3. Measuring time from Control Low to Y Valid

By simulation and observation, the times from control low/high to Y valid were measured to be: •  $t_{CLYV} = 137.792 \, ps$

•

$$t_{CHYV} = 232.677 \, ps$$

### 2. The D-Latch

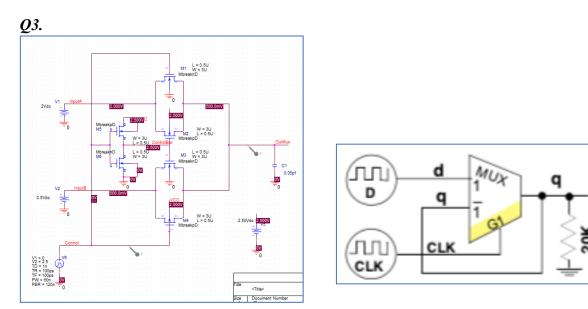

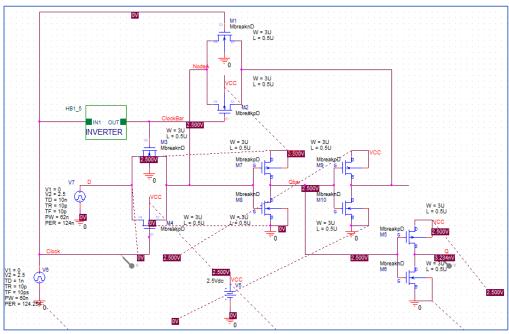

Fig 4. MUX Circuit schematic

Fig 5. D-Latch using MUX

Fig 6. D-Latch Circuit schematic with added parts

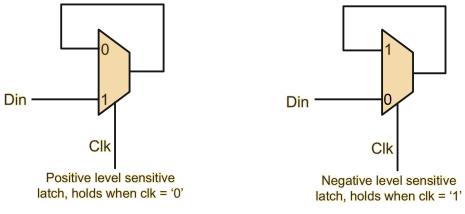

A 2:1 multiplexer selects between two inputs depending upon the value of its select input. Also, a latch holds its previous value when its enable pin is in a particular state ('0' for positive level sensitive latch and '1' for negative level sensitive latch). To achieve this, a connection was made from the output of the MUX (Qbar) to the 0 input, to create a feedback. Inverters were also added to Qbar to generate Q output. See figure below.

Fig 7. D-Latch created from MUX

Fig 8. Waveform showing transparent latching

### ELEC3500: Digital Electronics Lab 3

Q5.

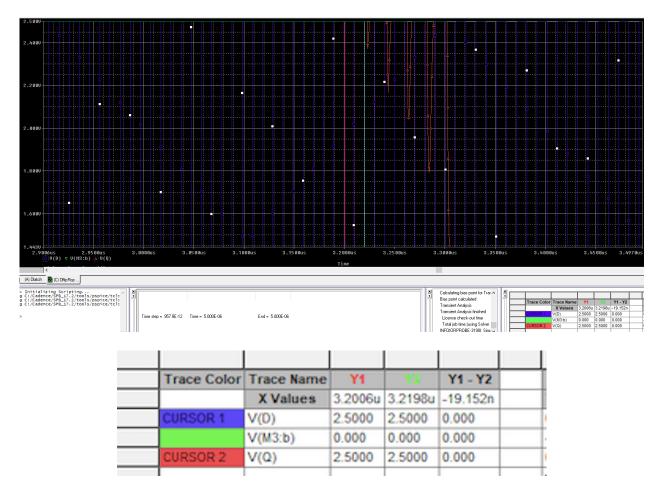

| Trace Color | Trace Name | ¥1      |         | Y1 - Y2  |

|-------------|------------|---------|---------|----------|

|             | X Values   | 3.7526u | 3.7619u | -9.3472n |

| CURSOR 1    | V(CLOCK)   | 0.000   | 0.000   | 0.000    |

| CURSOR 2    | V(Q)       | 13.005m | 15.089m | -2.0837m |

Fig 4. Measuring setup time for Latch circuit

Setup time is seen to be 9.347ns.

$\bigcirc$

#### ELEC3500: Digital Electronics Lab 3

Q6.

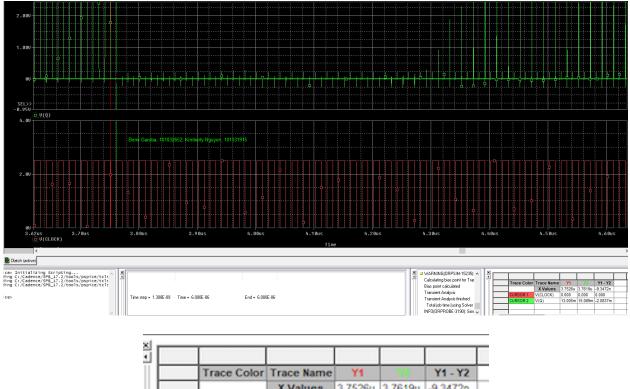

Fig 5. Measuring setup time for Latch circuit containing 0.5pF

Capacitor

The delay setup time was noticed to have increased by 10 ns on Fig 5.It is now 19.33ns

Fig 6. Measuring setup time for D flip-flop at the first invalid V<sub>out</sub> point

The setup time as shown is 19.152 s.

Fig 7. Measuring setup time for D flip-flop at the last valid V<sub>out</sub> point

The overall setup time I gotten by subtracting the setup time in Fig 7. From the time in Fig.6:

19.152ns - 2.4909ns = 16.66ns.