# Product Datasheet 800G QSFP112-DD DR8 Transceiver

## **Application**

- Data center & Networking Equipment

- Servers/Storage Devices

- High Performance Computing (HPC)

- Switches/Routers

- Telecom Central Offices (CO)

- Test and Measurement Equipment

## 1.0 Product Specification

## 1.1 Absolute Maximum Ratings (TC=25°C, unless otherwise noted)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings will cause permanent damage and/or adversely affect device reliability.

| Parameter                   | Symbol | Min  | Typical | Max                  | Unit       | Notes           |

|-----------------------------|--------|------|---------|----------------------|------------|-----------------|

| Storage Temperature         | TS     | -40  | -       | +85                  | $^{\circ}$ |                 |

| Maximum Supply Voltage      | Vcc    | -0.5 | -       | 3.6                  | V          |                 |

| Operating Relative Humidity | RH     | 5    | -       | 95                   | %          | No condensation |

| Control Input Voltage       | Vı     | -0.3 | -       | V <sub>CC</sub> +0.5 | V          |                 |

## 1.2 General Specifications (Tc=25°C, unless otherwise noted)

| Parameter                        | Symbol    | Min   | Typical | Max   | Unit         | Notes |

|----------------------------------|-----------|-------|---------|-------|--------------|-------|

| Operating Case Temperature       | $T_{OPR}$ | 0     | -       | 70    | $^{\circ}$ C |       |

| Power Supply Voltage             | Vcc       | 3.135 | 3.3     | 3.465 | V            |       |

| Maximum Power Dissipation        | $P_D$     | -     | 7.5     | 8     | W            |       |

|                                  |           |       |         |       |              |       |

| Signaling Rate per Lane          | SRL       | -     | 53.125  | ı     | GBd          | PAM4  |

| Two Wire Serial Interface Clock  | 1         | -100  | -       | 400   | kHz          |       |

| Rate                             |           |       |         |       |              |       |

| Power Supply Noise Tolerance     | -         | -     | -       | 66    | mV           |       |

| (10Hz - 10MHz)                   |           |       |         |       |              |       |

| Rx Differential Data Output Load | -         | -     | 100     | ı     | Ohm          |       |

| Operating Distance (MMF@OM3)     | -         | -     | -       | 60    | m            |       |

| Operating Distance (MMF@OM4)     | -         | -     | -       | 100   | m            |       |

## 1.3 Transmitter Characteristics (TC=25°C, unless otherwise noted)

| Parameter                                                                | Symbol           | Min    | Typical | Max    | Unit  | Notes |

|--------------------------------------------------------------------------|------------------|--------|---------|--------|-------|-------|

| Wavelength                                                               | $\lambda_{C}$    | 1304.5 | 1310    | 1317.5 | nm    |       |

| Side-mode suppression ratio (SMSR)                                       | SMSR             | 30     | -       | -      | nm    |       |

| Average Launch Power, each lane                                          | $AOP_L$          | -4.6   | -       | 4.0    | dBm   | 1     |

| Outer Optical Modulation<br>Amplitude (OMA <sub>outer</sub> ), each lane | T <sub>OMA</sub> | -2.6   |         | 3.5    | dBm   | 2     |

| Transmitter and Dispersion Eye<br>Closure for PAM4 (TDECQ), each<br>lane | TDECQ            | 1      | -       | 3.4    | dB    | 9     |

| Average Launch Power of OFF Transmitter, each lane                       | T <sub>OFF</sub> | ı      | -       | -30    | dBm   |       |

| Extinction Ratio, each lane                                              | ER               | 2.5    | 3.5     | -      | dB    |       |

| RIN <sub>14</sub> OMA                                                    | RIN              | -      |         | -132   | dB/Hz |       |

| Optical Return Loss Tolerance                                            | ORL              |        | -       | 17.1   | dB    |       |

| Transmitter Reflectance                                                  | T <sub>R</sub>   | -      | -       | -26    | dB    | 3     |

#### Notes

- 1. Average launch power, each lane (min) is informative and not the principal indicator of signal strength.

- 2. Even if max (TECQ, TDECQ) < 1.8dB, OMAouter (min) must exceed this value.

- 3. Transmitter reflectance is defined looking into the transmitter.

## 1.4 Receiver Characteristics (TC=25°C, unless otherwise noted)

| Parameter                                                        | Symbol        | Min    | Typical | Max   | Unit | Notes |

|------------------------------------------------------------------|---------------|--------|---------|-------|------|-------|

| Wavelength                                                       | $\lambda_{C}$ | 1304.5 | 1310    | 1317. | nm   |       |

|                                                                  |               |        |         | 5     |      |       |

| Damage Threshold, average optical power, each lane               | $AOP_D$       | 5      | 1       | 1     | dBm  |       |

| Average Receive Power, each                                      | $AOP_R$       | -6.3   |         | 4.0   | dBm  |       |

| lane                                                             | AOPR          | -0.5   | _       | 4.0   | иын  |       |

| Receive Power (OMA <sub>outer</sub> ), each                      | $OMA_R$       |        |         | 3.5   | dBm  |       |

| lane                                                             | OIVIAR        | =      | 1       | 5.5   | иын  |       |

| Receiver Reflectance                                             | RR            | -      | -       | -26   | dB   |       |

| Receiver Sensitivity (OMA <sub>outer</sub> ), each lane          | Soma          | -      | -       | -4.4  | dBm  | 1     |

| Stressed Receiver Sensitivity (OMA <sub>outer</sub> ), each lane | SRS           | -      |         | -2.5  | dBm  | 2     |

| Conditions of stressed receiver sensitivity test |                      |  |     |  |     |  |

|--------------------------------------------------|----------------------|--|-----|--|-----|--|

| Stressed eye closure for PAM4                    | SECQ                 |  | 4.4 |  | dB  |  |

| OMA <sub>outer</sub> of each aggressor lane      | OMA <sub>outer</sub> |  | 3.5 |  | dBm |  |

#### Notes

- 1. Receiver sensitivity (OMAouter), each lane (max) is informative and is defined for a transmitter with TDECQ<=1.8 dB

- 2. Measured with conformance test signal at TP3 for the BER = 2.4x10-4

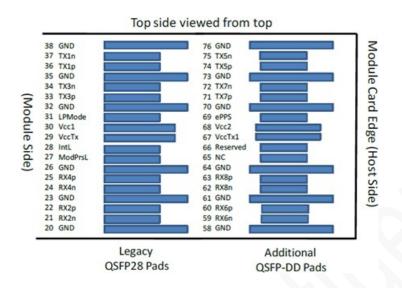

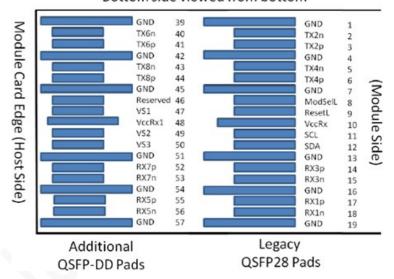

#### 1.5 PIN Descriptions

#### Bottom side viewed from bottom

| PAD | Logic | Symbol | Description                         | Plug<br>Seq⁴ | Notes |

|-----|-------|--------|-------------------------------------|--------------|-------|

| 1   |       | GND    | Ground                              | 1B           | 1     |

| 2   | CML-I | Tx2n   | Transmitter Inverted Data Input     | 3B           |       |

| 3   | CML-I | Tx2p   | Transmitter Non-Inverted Data Input | 3B           |       |

| 4   |       | GND    | Ground                              | 1B           | 1     |

| 5   | CML-I | Tx4n   | Transmitter Inverted Data Input     | 3B           |       |

## 800G QSFP112-DD DR8 Transceiver

| 6  | CML-I          | Тх4р        | Transmitter Non-Inverted Data Input | 3B |   |

|----|----------------|-------------|-------------------------------------|----|---|

| 7  |                | GND         | Ground                              | 1B | 1 |

| 8  | LVTTL-I        | ModSelL     | Module Select.                      | 3B |   |

| 9  | LVTTL-I        | ResetL      | Module Reset.                       | 3B |   |

| 10 |                | VccRx       | +3.3V Power Supply Receiver         | 2B | 2 |

| 11 | LVCMOS-I/<br>O | SCL         | 2-wire serial interface clock       | 3B |   |

| 12 | LVCMOS-I/<br>O | SDA         | 2-wire serial interface data        | 3B |   |

| 13 |                | GND         | Ground                              | 1B | 1 |

| 14 | CML-O          | Rx3p        | Receiver Non-Inverted Data Output   | 3B |   |

| 15 | CML-O          | Rx3n        | Receiver Inverted Data Output       | 3B |   |

| 16 |                | GND         | Ground                              | 1B | 1 |

| 17 | CML-O          | Rx1p        | Receiver Non-Inverted Data Output   | 3B |   |

| 18 | CML-O          | Rx1n        | Receiver Inverted Data Output       | 3B |   |

| 19 |                | GND         | Ground                              | 1B | 1 |

| 20 |                | GND         | Ground                              | 1B | 1 |

| 21 | CML-O          | Rx2n        | Receiver Inverted Data Output       | 3B |   |

| 22 | CML-O          | Rx2p        | Receiver Non-Inverted Data Output   | 3B |   |

| 23 |                | GND         | Ground                              | 1B | 1 |

| 24 | CML-O          | Rx4n        | Receiver Inverted Data Output       | 3B |   |

| 25 | CML-O          | Rx4p        | Receiver Non-Inverted Data Output   | 3B |   |

| 26 |                | GND         | Ground                              | 1B | 1 |

| 27 | LVTTL-O        | ModPrs<br>L | Module Present.                     | 3B |   |

| 28 | LVTTL-O        | IntL        | Interrupt.                          | 3B |   |

| 29 |                | VccTx       | +3.3V Power supply transmitter      | 2B | 2 |

| 30 |                | Vcc1        | +3.3V Power supply                  | 2B | 2 |

| 31 | LVTTL-I        | LPMode      | Low Power Mode                      | 3B |   |

| 32 |                | GND         | Ground                              | 1B | 1 |

| 33 | CML-I          | Тх3р        | Transmitter Non-Inverted Data Input | 3B |   |

| 34 | CML-I          | Tx3n        | Transmitter Inverted Data Input     | 3B |   |

| 35 |                | GND         | Ground                              | 1B | 1 |

| 36 | CML-I          | Tx1p        | Transmitter Non-Inverted Data Input | 3B |   |

| 37 | CML-I          | Tx1n        | Transmitter Inverted Data Input     | 3B |   |

| 38 |                | GND         | Ground                              | 1B | 1 |

| 39 |                | GND         | Ground                              | 1A | 1 |

| 40 | CML-I          | Tx6n        | Transmitter Inverted Data Input     | 3A |   |

## 800G QSFP112-DD DR8 Transceiver

| 41 | CML-I   | Тх6р    | Transmitter Non-Inverted Data Input                 | 3A       |   |

|----|---------|---------|-----------------------------------------------------|----------|---|

| 42 |         | GND     | Ground                                              | 1A       | 1 |

| 43 | CML-I   | Tx8n    | Transmitter Inverted Data Input                     | 3A       |   |

| 44 | CML-I   | Tx8p    | Transmitter Non-Inverted Data Input                 |          |   |

| 45 |         | GND     | Ground                                              | 3A<br>1A | 1 |

| 46 |         | Reserve | For future use                                      | 3A       | 3 |

|    |         | d       |                                                     |          |   |

| 47 |         | VS1     | Module Vendor Specific 1                            | 3A       | 3 |

| 48 |         | VccRx1  | 3.3V Power Supply                                   | 2A       | 2 |

| 49 |         | VS2     | Module Vendor Specific 2                            | 3A       |   |

| 50 |         | VS3     | Module Vendor Specific 3                            | 3A       |   |

| 51 |         | GND     | Ground                                              | 1A       | 1 |

| 52 | CML-O   | Rx7p    | Receiver Non-Inverted Data Output                   | 3A       |   |

| 53 | CML-O   | Rx7n    | Receiver Inverted Data Output                       | 3A       |   |

| 54 |         | GND     | Ground                                              | 1A       | 1 |

| 55 | CML-O   | Rx5p    | Receiver Non-Inverted Data Output                   | 3A       |   |

| 56 | CML-O   | Rx5n    | Receiver Inverted Data Output                       | 3A       |   |

| 57 |         | GND     | Ground                                              | 1A       | 1 |

| 58 |         | GND     | Ground                                              | 1A       | 1 |

| 59 | CML-O   | Rx6n    | Receiver Inverted Data Output                       | 3A       |   |

| 60 | CML-O   | Rx6p    | Receiver Non-Inverted Data Output                   | 3A       |   |

| 61 |         | GND     | Ground                                              | 1A       | 1 |

| 62 | CML-O   | Rx8n    | Receiver Inverted Data Output                       | 3A       |   |

| 63 | CML-O   | Rx8p    | Receiver Non-Inverted Data Output                   | 3A       |   |

| 64 |         | GND     | Ground                                              | 1A       | 1 |

| 65 |         | NC      | No Connect                                          | 3A       | 3 |

| 66 |         | Reserve | For future use                                      | 3A       | 3 |

|    |         | d       |                                                     |          |   |

| 67 |         | VccTx1  | 3.3V Power Supply                                   | 2A       | 2 |

| 68 |         | Vcc2    | 3.3V Power Supply                                   | 2A       | 2 |

| 69 | LVTTL-I | ePPS    | Precision Time Protocol (PTP) reference clock input | 3A       | 3 |

| 70 |         | GND     | Ground                                              | 1A       | 1 |

| 71 | CML-I   | Тх7р    | Transmitter Non-Inverted Data Input                 | 3A       |   |

| 72 | CML-I   | Tx7n    | Transmitter Inverted Data Input                     | 3A       |   |

| 73 |         | GND     | Ground                                              | 1A       | 1 |

| 74 | CML-I   | Тх5р    | Transmitter Non-Inverted Data Input                 | 3A       |   |

| 75 | CML-I   | Tx5n    | Transmitter Inverted Data Input                     | 3A       |   |

#### 800G QSFP112-DD DR8 Transceiver

| 76 GND Grour | u I IA | 1 |

|--------------|--------|---|

|--------------|--------|---|

#### Notes:

- [1] QSFP-DD uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

- [2] VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the host side of the Host Card Edge Connector are listed in Table 7. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The connector Vcc pins are each rated for a maximum current of 1000 mA.

- [3] All Vendor Specific, Reserved, No Connect and ePPS (if not used) pins may be terminated with 50 Ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF.

- [4] Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B (see Figure 2 for pad locations). Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A,1B will then occur simultaneously, followed by 2A,2B, followed by 3A, 3B.

#### 2.0 Product Information

| Data Rate | Factor     |     | Optical | Wavelength | Reach |

|-----------|------------|-----|---------|------------|-------|

| 800G      | QSFP112-DD | DR8 | MPO     | 1310nm     | 500m  |

#### **ESD Safety Cautionsy**

This transceiver is specified as ESD threshold 1KV for high speed data pins based on Human Body Model per ANSI/ESDA/JEDECJS-001. The units are subjected to 15kV air discharges during operation and 8kV direct contact discharges to the case. However, normal ESD precautions are still required during the handling of this module. This transceiver is shipped in ESD protective packaging. It should be removed from the packaging and handled only in an ESD protected environment.

#### **Important Notice**

The performance figures, data, and any illustrative material presented in this datasheet are typical and must be explicitly confirmed in writing by Quantex before they are deemed applicable to any specific order or contract.

By Quantex's policy of continuous improvement, specifications may change without prior notice. The publication of information in this datasheet does not imply exemption from patent or other protective rights held by Quantex or other parties.

E-mail: sales@quantextech.com Official Site: www.quantextech.com

### 3.0 Revision Record

| Rev. | Comments        | Date |

|------|-----------------|------|

| A01  | Initial Release |      |

|      |                 |      |

|      |                 |      |

|      |                 |      |