| AV Mathematics-II              | I for EC Engineering | Semester    | 3   |

|--------------------------------|----------------------|-------------|-----|

| Course Code                    | BMATEC301            | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:0:0              | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40                   | Total Marks | 100 |

| Credits                        | 03                   | Exam Hours  | 03  |

| Examination type (SEE)         | Theory               |             |     |

- Learn to use the Fourier series to represent periodical physical phenomena in engineering analysis and to enable the student to express non-periodic functions to periodic functions using the Fourier series and Fourier transforms.

- Analyze signals in terms of Fourier transforms

- Develop the knowledge of solving differential equations and their applications in Electronics & Communication engineering.

- To find the association between attributes and the correlation between two variables

# **Teaching-Learning Process**

# **Pedagogy (General Instructions):**

These are sample Strategies, teachers can use to accelerate the attainment of the various course outcomes.

- 1. In addition to the traditional lecture method, different types of innovative teaching methods may be adopted so that the delivered lessons shall develop students' theoretical and applied Mathematical skills.

- 2. State the need for Mathematics with Engineering Studies and Provide real-life examples.

- 3. Support and guide the students for self–study.

- 4. You will assign homework, grading assignments and quizzes, and documenting students' progress.

- 5. Encourage the students to group learning to improve their creative and analytical skills.

- 6. Show short related video lectures in the following ways:

- As an introduction to new topics (pre-lecture activity).

- As a revision of topics (post-lecture activity).

- As additional examples (post-lecture activity).

- As an additional material of challenging topics (pre-and post-lecture activity).

- As a model solution of some exercises (post-lecture activity).

## Module-1: Fourier series and practical harmonic analysis

Periodic functions, Dirichlet's condition. Fourier series expansion of functions with period  $2\pi$  and with arbitrary period: periodic rectangular wave, Half-wave rectifier, rectangular pulse, Saw tooth wave. Half-range Fourier series. Triangle and half range expansions, Practical harmonic analysis, variation of periodic current. (8 hours)

### (RBT Levels: L1, L2 and L3)

#### **Module-2: Infinite Fourier Transforms**

Infinite Fourier transforms, Fourier cosine and sine transforms, Inverse Fourier transforms, Inverse Fourier cosine and sine transforms, discrete Fourier transform (DFT), Fast Fourier transform (FFT). (8 hours)

# (RBT Levels: L1, L2 and L3)

# **Module-3: Z Transforms**

Definition, Z-transforms of basic sequences and standard functions. Properties: Linearity, scaling, first and second shifting, multiplication by n. Initial and final value theorem. Inverse Z- transforms. Application to difference equations. (8 hours)

(RBT Levels: L1, L2 and L3)

# Module-4: Ordinary Differential Equations of Higher Order

Higher-order linear ODEs with constant coefficients - Inverse differential operator, problems.Linear differential equations with variable Coefficients-Cauchy's and Legendre's differential equations—Problems. Application of linear differential equations to L-C circuit and L-C-R circuit.(8 hours)

(RBT Levels: L1, L2 and L3)

# Module-5: Curve fitting, Correlation, and Regressions

Principles of least squares, Curve fitting by the method of least squares in the form y = a + bx,  $y = a + bx + cx^2$ , and  $y = ax^b$ . Correlation, Coefficient of correlation, Lines of regression, Angle between regression lines, standard error of estimate, rank correlation.

### **Course outcome (Course Skill Set)**

(RBT Levels: L1, L2 and L3)(8 hours)

At the end of the course, the student will be able to:

- 1. Demonstrate the Fourier series to study the behavior of periodic functions and their applications in system communications, digital signal processing, and field theory.

- 2. To use Fourier transforms to analyze problems involving continuous-time signals

- 3. To apply Z-Transform techniques to solve difference equations

- 4. Understand that physical systems can be described by differential equations and solve such equations

- 5. Make use of correlation and regression analysis to fit a suitable mathematical model for statistical data

# **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

# **Continuous Internal Evaluation:**

- There are 25 marks for the CIE's Assignment component and 25 for the Internal Assessment Test component.

- Each test shall be conducted for 25 marks. The first test will be administered after 40-50% of the coverage of the syllabus, and the second test will be administered after 85-90% of the coverage of the syllabus. The average of the two tests shall be scaled down to 25 marks

- Any two assignment methods mentioned in the 22OB2.4, if an assignment is project-based then only one assignment for the course shall be planned. The schedule for assignments shall be planned properly by the course teacher. The teacher should not conduct two assignments at the end of the semester if two assignments are planned. Each assignment shall be conducted for 25 marks. (If two assignments are conducted then the sum of the two assignments shall be scaled down to 25 marks)

- The final CIE marks of the course out of 50 will be the sum of the scale-down marks of tests and assignment/s marks.

# Internal Assessment Test question paper is designed to attain the different levels of Bloom's taxonomy as per the outcome defined for the course.

#### **Semester-End Examination:**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (duration 03 hours).

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

- 3. The students have to answer 5 full questions, selecting one full question from each module.

- 4. Marks scored shall be proportionally reduced to 50 marks

# **Suggested Learning Resources:**

# Books (Name of the author/Title of the Book/Name of the publisher/Edition and Year) Text Books:

- 1. **B. S. Grewal**: "Higher Engineering Mathematics", Khanna Publishers, 44<sup>th</sup>Ed., 2021.

- 2. E. Kreyszig: "Advanced Engineering Mathematics", John Wiley & Sons, 10<sup>th</sup>Ed., 2018.

#### **Reference Books:**

- 1. V. Ramana: "Higher Engineering Mathematics" McGraw-Hill Education, 11<sup>th</sup>Ed., 2017

- 2. **Srimanta Pal & Subodh C.Bhunia**: "Engineering Mathematics" Oxford University Press, 3<sup>rd</sup>Ed., 2016.

- 3. **N.P Bali and Manish Goyal**: "A Textbook of Engineering Mathematics" Laxmi Publications, 10<sup>th</sup>Ed., 2022.

- 4. **C. Ray Wylie, Louis C. Barrett:** "Advanced Engineering Mathematics" McGraw-Hill Book Co., New York, 6<sup>th</sup>Ed., 2017.

- 5. **Gupta C.B, Sing S.R and Mukesh Kumar:** "Engineering Mathematic for Semester I and II", McGraw Hill Education(India) Pvt. Ltd 2015.

- 6. **H.K. Dass and Er. Rajnish Verma:** "Higher Engineering Mathematics" S.Chand Publication, 3<sup>rd</sup>Ed.,2014.

- 7. **James Stewart:** "Calculus" Cengage Publications, 7<sup>th</sup>Ed., 2019.

# Web links and Video Lectures (e-Resources):

- http://nptel.ac.in/courses.php?disciplineID=111

- http://www.class-central.com/subject/math(MOOCs)

- http://academicearth.org/

- VTU e-Shikshana Program

- VTU EDUSAT Program.

# Activity-Based Learning (Suggested Activities in Class)/Practical-Based Learning

- Ouizzes

- Assignments

- Seminar

| Digital System De              | sign using Verilog               | Semester    | 3   |

|--------------------------------|----------------------------------|-------------|-----|

| Course Code                    | BEC302                           | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:2                            | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40 hours Theory + 8-10 Lab slots | Total Marks | 100 |

| Credits                        | 04                               | Exam Hours  | 03  |

| Examination nature (SEE)       | Theory/Prac                      | tical       |     |

This course will enable students to:

- To impart the concepts of simplifying Boolean expression using K-map techniques and Quine-McCluskey minimization techniques.

- To impart the concepts of designing and analyzing combinational logic circuits.

- To impart design methods and analysis of sequential logic circuits.

- To impart the concepts of Verilog HDL-data flow and behavioural models for the design of digital systems.

### **Teaching-Learning Process (General Instructions)**

These are sample Strategies, which teacher can use to accelerate the attainment of the various course outcomes.

- Lecture method (L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- Show Video/animation films to explain the different concepts of Linear Algebra & Signal Processing.

- Encourage collaborative (Group) Learning in the class.

- Ask at least three HOTS (Higher order Thinking)questions in the class, which promotes critical thinking.

- Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyze information rather than simply recall it.

- Topics will be introduced in a multiple representation.

- Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

- Discuss how every concept can be applied to the real world-and when that's possible, it helps improve the students' understanding.

- Adopt Flipped class technique by sharing the materials/Sample Videos prior to the class and have discussions on the topic in the succeeding classes.

- Give Programming Assignments.

#### **MODULE-1**

**Principles of Combinational Logic**: Definition of combinational logic, Canonical forms, Generation of switching equations from truth tables, Karnaugh maps-up to 4 variables, Quine-McCluskey Minimization

Technique. Quine-McCluskey using Don't CareTerms.(Section3.1to3.5ofText1).

#### **MODULE-2**

**Logic Design with MSI Components and Programmable Logic Devices**: Binary Adders and Subtractors, Comparators, Decoders, Encoders, Multiplexers, Programmable Logic Devices(PLDs) (Section 5.1 to 5.7 of Text 2)

### **MODULE-3**

**Flip-Flops and its Applications**: The Master-Slave Flip-flops(Pulse-Triggered flip-flops):SR flip-flops, JK flip flops, Characteristic equations, Registers, Binary Ripple Counters, Synchronous Binary Counters, Counters based on Shift Registers, Design of Synchronous mod-n Counter using clocked T, J K, D and SR flip-flops.(Section 6.4, 6.6 to 6.9 (Excluding 6.9.3)of Text2)

#### **MODULE-4**

**Introduction to Verilog**: Structure of Verilog module, Operators, Data Types, Styles of Description. (Section1.1to1.6.2, 1.6.4 (only Verilog), 2 of Text 3)

**Verilog Data flow description:** Highlights of Data flow description, Structure of Data flow description.(Section2.1to2.2(only Verilog) of Text3)

#### **MODULE-5**

**Verilog Behavioral description**: Structure, Variable Assignment Statement, Sequential Statements, Loop Statements, Verilog Behavioral Description of Multiplexers (2:1, 4:1, 8:1). (Section 3.1 to 3.4 (onlyVerilog) of Text 3)

**Verilog Structural description**: Highlights of Structural description, Organization of structural description, Structural description of ripple carry adder. (Section 4.1 to 4.2 of Text 3)

**PRACTICAL COMPONENT OF IPCC** (Experiments can be conducted either using any circuit simulation software or discrete components)

| Sl.N | Experiments                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | To simplify the given Boolean expressions and realize using Verilog program                                                                              |

| 2    | To realize Adder/Subtractor(Full/half)circuits using Verilog data flow description.                                                                      |

| 3    | To realize 4-bit ALU using Verilog program.                                                                                                              |

| 4    | To realize the following Code converters using Verilog Behavioral description                                                                            |

|      | a)Gray to binary and vice versa b)Binary to excess3 and vice versa                                                                                       |

| 5    | To realize using Verilog Behavioral description:8:1mux, 8:3encoder, Priority encoder                                                                     |

| 6    | To realize using Verilog Behavioral description:1:8Demux, 3:8 decoder,2 –bit Comparator                                                                  |

| 7    | To realize using Verilog Behavioral description:                                                                                                         |

|      | Flip-flops: a)JK type b)SR type c)T type and d)D type                                                                                                    |

| 8    | To realize Counters-up/down (BCD and binary)using Verilog Behavioral description.                                                                        |

|      | nstration Experiments (For CIE only–not to be included for SEE) PGA/CPLD kits for down loading Verilog codes and check the output for interfacing ments. |

| 9    | Verilog Program to interface a Stepper motor to the FPGA/CPLD and rotate the motor in the specified direction (by N steps).                              |

| 10   | Verilog programs to interface Switches and LEDs to the FPGA/CPLD and demonstrate its working.                                                            |

#### **Course outcomes (Course Skill Set):**

At the end of the course the student will be able to:

- 1. Simplify Boolean functions using K-map and Quine-McCluskey minimization technique.

- 2. Analyze and design for combinational logic circuits.

- 3. Analyze the concepts of Flip Flops(SR, D,T and JK) and to design the synchronous sequential circuits using Flip Flops.

- 4. Model Combinational circuits (adders, subtractors, multiplexers) and sequential circuits using Verilog descriptions.

#### **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

The IPCC means the practical portion integrated with the theory of the course. CIE marks for the theory component are **25 marks** and that for the practical component is **25 marks**.

# CIE for the theory component of the IPCC

- 25 marks for the theory component are split into **15 marks** for two Internal Assessment Tests (Two Tests, each of 15 Marks with 01-hour duration, are to be conducted) and **10 marks** for other assessment methods mentioned in 22OB4.2. The first test at the end of 40-50% coverage of the syllabus and the second test after covering 85-90% of the syllabus.

- Scaled-down marks of the sum of two tests and other assessment methods will be CIE marks for the theory component of IPCC (that is for **25 marks**).

- The student has to secure 40% of 25 marks to qualify in the CIE of the theory component of IPCC.

# CIE for the practical component of the IPCC

- 15 marks for the conduction of the experiment and preparation of laboratory record, and 10 marks for the test to be conducted after the completion of all the laboratory sessions.

- On completion of every experiment/program in the laboratory, the students shall be evaluated including viva-voce and marks shall be awarded on the same day.

- The CIE marks awarded in the case of the Practical component shall be based on the continuous evaluation of the laboratory report. Each experiment report can be evaluated for 10 marks. Marks of all experiments' write-ups are added and scaled down to **15 marks**.

- The laboratory test (**duration 02/03 hours**) after completion of all the experiments shall be conducted for 50 marks and scaled down to **10 marks**.

- Scaled-down marks of write-up evaluations and tests added will be CIE marks for the laboratory component of IPCC for **25 marks**.

- The student has to secure 40% of 25 marks to qualify in the CIE of the practical component of the IPCC.

# **SEE for IPCC**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (**duration 03 hours**)

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

- 3. The students have to answer 5 full questions, selecting one full question from each module.

- 4. Marks scored by the student shall be proportionally scaled down to 50 Marks

# The theory portion of the IPCC shall be for both CIE and SEE, whereas the practical portion will have a CIE component only. Questions mentioned in the SEE paper may include questions from the practical component.

• The minimum marks to be secured in CIE to appear for SEE shall be 10 (40% of maximum marks-25) in the theory component and 10 (40% of maximum marks -25) in the practical component. The laboratory component of the IPCC shall be for CIE only. However, in SEE, the questions from the laboratory component shall be included. The maximum of 04/05 subquestions are to be set from the practical component of IPCC, the total marks of all questions

- should not be more than 20 marks.

- SEE will be conducted for 100 marks and students shall secure 35% of the maximum marks to qualify for the SEE. Marks secured will be scaled down to 50.

- The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

# **Suggested Learning Resources:**

#### **Books**

- 1. Digital Logic Applications and Design by John MYarbrough, Thomson Learning, 2001.

- 2. Digital Principles and Design by Donald DGivone, McGrawHill, 2002.

- 3. HDL Programming VHDL and Verilog by Nazeih M Botros, 2009 reprint, Dream techpress.

#### ReferenceBooks:

- 1. Fundamentals of logic design, by Charles H Roth Jr., Cengage Learning

- 2. Logic Design, by Sudhakar Samuel, Pearson/Sanguine, 2007

- 3. Fundamentals of HDL, by Cyril PR, Pearson/Sanguine 2010

# Web links and Video Lectures (e-Resources):

Activity Based Learning (Suggested Activities in Class)/ Practical Based learning

Programming Assignments/Mini Projects can be given to improve programming skills.

| Electronic Pr                  | inciples and Circuits            | Semester        | 3   |

|--------------------------------|----------------------------------|-----------------|-----|

| Course Code                    | BEC303                           | CIE Marks       | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:2                            | SEE Marks       | 50  |

| Total Hours of Pedagogy        | 40 hours Theory + 8-10 Lab slots | Total Marks     | 100 |

| Credits                        | 04                               | Exam Hours      |     |

| Examination nature (SEE)       | Theory/Practical/Viva-Voce /T    | erm-work/Others |     |

This course will enable students to

- Design and analyse the BJT circuits as an amplifier and voltage regulation.

- Design of MOSFET Amplifiers and analyse the basic amplifier configurations using small signal equivalent circuit models

- Design of operational amplifiers circuits as Comparators, DAC and filters.

- Understand the concept of positive and negative feedback.

- Analyze Power amplifier circuits in different modes of operation.

- Construct Feedback and Oscillator circuits using FET.

- Understand the thyristor operation and the different types of thyristors.

#### **Teaching-Learning Process (General Instructions)**

These are sample Strategies, which teacher can use to accelerate the attainment of the various course outcomes.

- 1. Lecture method (L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- 2. Show Video/animation films to explain evolution of communication technologies.

- 3. Encourage collaborative (Group) Learning in the class

- 4.Ask at least three HOTS (Higher order Thinking) questions in the class, which promotes critical thinking

- 5. Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyze information rather than simply recall it.

- 6. Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

- 7. Discuss how every concept can be applied to the real world and when that's possible, it helps improve the students' understanding.

#### **MODULE-1**

**Transistor Biasing:** Voltage Divider Bias, VDB Analysis, VDB Load line and Q point, Two supply Emitter Bias, Other types of Bias.

**BJT AC models**: Base Biased Amplifier, Emitter Biased Amplifier, Small Signal Operation, AC Beta, AC Resistance of the emitter diode, Two transistor models, Analyzing an amplifier, H parameters, Relations between R and H parameters.

**Voltage Amplifiers**: Voltage gain, Loading effect of Input Impedance.

**CC Amplifiers:** CC Amplifier, Output Impedance.

[Text1]

#### **MODULE-2**

#### **MOSFET**

Biasing in MOS amplifier circuits: Fixing VGS, Fixing VG, Drain to Gate feedback resistor.

Small signal operation and modelling: The DC bias point, signal current in drain, voltage gain, small signal equivalent circuit models, transconductance, The T equivalent circuit model.

MOSFET Amplifier configuration: Basic configurations, characterizing amplifiers, CS amplifier with and without source resistance, The Common Gate Amplifier, Source follower.

[Text 2]

#### **MODULE-3**

**Linear Opamp Circuits:** Summing Amplifier and D/A Converter, Nonlinear Op-amp Circuits: Comparator with zero reference, Comparator with non-zero references. Comparator with Hysteresis.

**Oscillator:** Theory of Sinusoidal Oscillation, The Wein-Bridge Oscillator, RC Phase Shift Oscillator, The Colpitts Oscillator, Hartley Oscillator, Crystal Oscillator.

**The 555 timer**: Monostable Operation, Astable Operation.

[Text1]

#### **MODULE-4**

**Negative Feedback:** Four Types of Negative Feedback, VCVS Voltage gain, Other VCVS Equations, ICVS Amplifier, VCIS Amplifier, ICIS Amplifier (No Mathematical Derivation).

**Active Filters:** Ideal Responses, First Order Stages, VCVS Unity Gain Second Order Low pass Filters, VCVS Equal Component Low Pass Filters, VCVS High Pass Filters, MFB Bandpass Filters, Bandstop Filters. [Text1]

#### **MODULE-5**

**Power Amplifiers:** Amplifier terms, Two load lines, Class A Operation, Class B operation, Class B push pull emitter follower, Class C Operation.

**Thyristors:** The four layer Diode, SCR, SCR Phase control, Bidirectional Thyristors, IGBTs, Other Thyristors. [Text1]

**PRACTICAL COMPONENT OF IPCC** (Experiments can be conducted either using any circuit simulation

*software or discrete components)*

| Sl.NO | Experiments                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

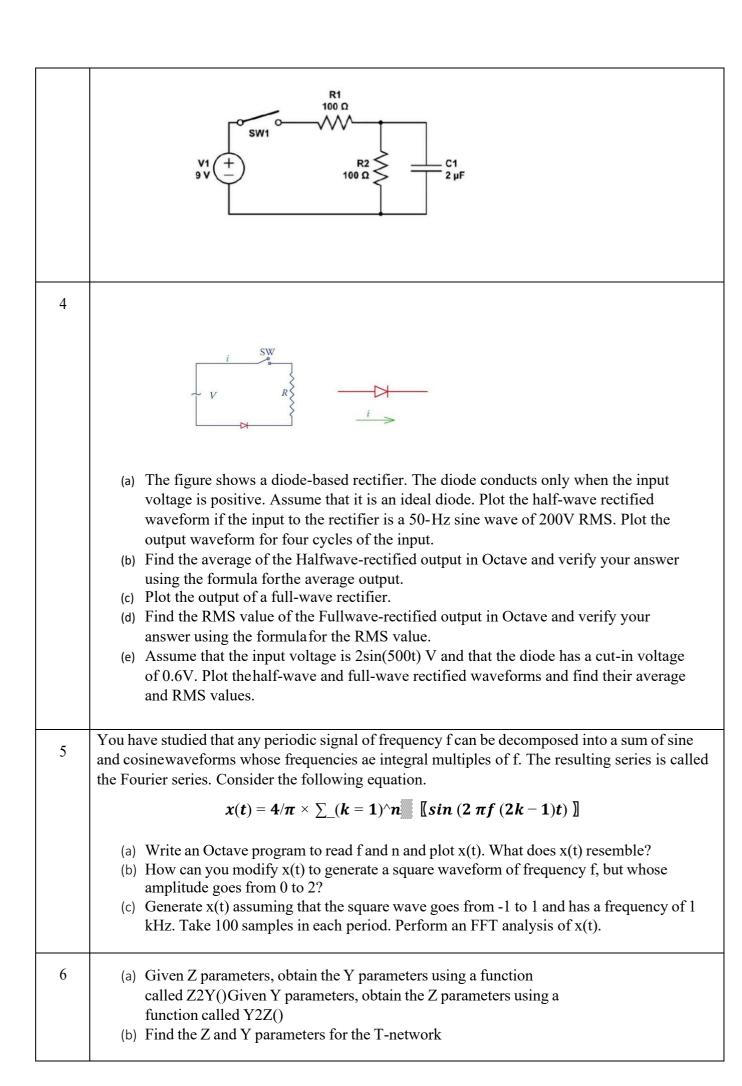

| 1     | Design and Test  (i) Bridge Rectifier with Capacitor Input Filter  (ii) Zener voltage regulator                                                                      |

| 2     | Design and Test Biased Clippers – a)Positive, b) Negative, c) Positive-Negative Positive and Negative Clampers with and without Reference.                           |

| 3     | Plot the transfer and drain characteristics of a JFET and calculate its drain resistance, mutual conductance and amplification factor.                               |

| 4     | Plot the transfer and drain characteristics of n-channel MOSFET and calculate its parameters, namely; drain resistance, mutual conductance and amplification factor. |

| 5     | Design and test Emitter Follower                                                                                                                                     |

| 6     | Design and plot the frequency response of Common Source JFET/MOSFET amplifier                                                                                        |

| 7     | Test the Opamp Comparator with zero and non zero reference and obtain the Hysteresis curve.                                                                          |

| 8     | Design and test Full wave Controlled rectifier using RC triggering circuit.                                                                                          |

| 9     | Design and test Precision Half wave and full wave rectifiers using Opamp                                                                                             |

| 10    | Design and test RC phase shift oscillator                                                                                                                            |

#### **Course outcomes (Course Skill Set):**

At the end of the course, the student will be able to:

- 1. Understand the characteristics of BJTs and FETs for switching and amplifier circuits.

- 2. Design and analyze amplifiers and oscillators with different circuit configurations and biasing conditions.

- 3. Understand the feedback topologies and approximations in the design of amplifiers and oscillators.

- 4. Design of circuits using linear ICs for wide range applications such as ADC, DAC, filters and timers.

- 5. Understand the power electronic device components and its functions for basic power electronic circuits.

#### **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

The IPCC means the practical portion integrated with the theory of the course. CIE marks for the theory component are **25 marks** and that for the practical component is **25 marks**.

#### CIE for the theory component of the IPCC

• 25 marks for the theory component are split into **15 marks** for two Internal Assessment Tests (Two Tests, each of 15 Marks with 01-hour duration, are to be conducted) and **10 marks** for other assessment methods mentioned in 220B4.2. The first test at the end of 40-50% coverage of the syllabus and the second test after covering 85-90% of the syllabus.

- Scaled-down marks of the sum of two tests and other assessment methods will be CIE marks for the theory component of IPCC (that is for **25 marks**).

- The student has to secure 40% of 25 marks to qualify in the CIE of the theory component of IPCC.

#### CIE for the practical component of the IPCC

- **15 marks** for the conduction of the experiment and preparation of laboratory record, and **10 marks** for the test to be conducted after the completion of all the laboratory sessions.

- On completion of every experiment/program in the laboratory, the students shall be evaluated including vivavoce and marks shall be awarded on the same day.

- The CIE marks awarded in the case of the Practical component shall be based on the continuous evaluation of

the laboratory report. Each experiment report can be evaluated for 10 marks. Marks of all experiments' writeups are added and scaled down to 15 marks.

- The laboratory test (duration 02/03 hours) after completion of all the experiments shall be conducted for 50 marks and scaled down to 10 marks.

- Scaled-down marks of write-up evaluations and tests added will be CIE marks for the laboratory component of IPCC for 25 marks.

- The student has to secure 40% of 25 marks to qualify in the CIE of the practical component of the IPCC.

#### **SEE for IPCC**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (duration 03 hours)

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

- 3. The students have to answer 5 full questions, selecting one full question from each module.

- 4. Marks scored by the student shall be proportionally scaled down to 50 Marks

# The theory portion of the IPCC shall be for both CIE and SEE, whereas the practical portion will have a CIE component only. Questions mentioned in the SEE paper may include questions from the practical component.

- The minimum marks to be secured in CIE to appear for SEE shall be 10 (40% of maximum marks-25) in the theory component and 10 (40% of maximum marks -25) in the practical component. The laboratory component of the IPCC shall be for CIE only. However, in SEE, the questions from the laboratory component shall be included. The maximum of 04/05 sub-questions are to be set from the practical component of IPCC, the total marks of all questions should not be more than 20 marks.

- SEE will be conducted for 100 marks and students shall secure 35% of the maximum marks to qualify for the SEE. Marks secured will be scaled down to 50.

- The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

### **Suggested Learning Resources:**

#### **Books**

- **1.** Albert Malvino, David J Bates, Electronic Principles, 7<sup>th</sup> Edition, Mc Graw Hill Education, 2017, ISBN:978-0-07-063424-4.

- 2. Microelectronic Circuits, Theory and Applications, Adel S Sedra, Kenneth C Smith, 6thEdition, Oxford, 2015.ISBN:978-0-19-808913-1

### Web links and Video Lectures (e-Resources):

- 1. Integrated Electronics: Analog and Digital Circuits and Systems, Jacob Millman, Christos C. Halkias, McGraw-Hill, 2015.

- 2. Electronic Devices and Circuit, Boylestad & Nashelsky, Eleventh Edition, Pearson, January 2015.

| <b>Activity Based</b> | <b>Learning (Suggested</b> | Activities in Class)/ | ' Practical Based learning |

|-----------------------|----------------------------|-----------------------|----------------------------|

|                       |                            |                       |                            |

| Network                        | x Analysis | Semester    | 3   |

|--------------------------------|------------|-------------|-----|

| Course Code                    | BEC304     | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:0      | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40         | Total Marks | 100 |

| Credits                        | 03         | Exam Hours  | 3   |

| Examination type (SEE)         | Theory     |             |     |

- 1. Apply mesh and nodal techniques to solve an electrical network.

- 2. Solve different problems related to Electrical circuits using Network Theorems and Two port network.

- 3. Familiarize with the use of Laplace transforms to solve network problems.

- 4. Study two port network parameters and their applications.

- 5. Study of RLC Series and parallel tuned circuit.

#### **Teaching-Learning Process (General Instructions)**

These are sample Strategies, which teachers can use to accelerate the attainment of the various course outcomes.

These are sample Strategies, which teacher can use to accelerate the attainment of the various course outcomes.

- Lecture method (L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- Encourage collaborative (Group)Learning in the class.

- Ask at least three HOTS(Higher order Thinking)questions in the class, which promotes critical thinking.

- Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyze information rather than simply recall it.

- Topics will be introduced in a multiple representation.

- Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

- Discuss how every concept can be applied to the real world-and when that's possible, it helps improve the students' understanding.

- Adopt Flipped class technique by sharing the materials/Sample Videos prior to the class and have discussions on the topic in the succeeding classes.

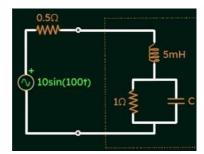

#### Module-1

**Basic Concepts:** Practical sources, Source transformations, Network reduction using Star - Delta transformation, Loop and node analysis with linearly dependent and independent sources for DC and AC networks.

#### Module-2

**Network Theorems:** Superposition, Millman's theorems, Thevenin's and Norton's theorems, Maximum Power transfer theorem.

#### Module-3

**Transient behavior and initial conditions:** Behavior of circuit elements under switching condition and their Representation, evaluation of initial and final conditions in RL, RC and

RLC circuits for AC and DC excitations.

#### **Module-4**

**Laplace Transformation & Applications:** Solution of networks, step, ramp and impulse responses, waveform Synthesis.

### **Module-5**

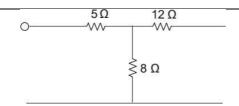

**Two port network parameters:** Definition of Z,Y, h and Transmission parameters, modelling with these parameters, relationship between parameters sets.

#### **Resonance:**

**Series Resonance:** Variation of Current and Voltage with Frequency, SelectivityandBandwidth,Q-Factor,CircuitMagnificationFactor,Selectivity with Variable Capacitance, Selectivity with Variable Inductance.

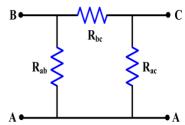

**Parallel Resonance:** Selectivity and Bandwidth, Maximum Impedance Conditions with C, Land f Variable, current in Anti-Resonant Circuit, The General Case-Resistance Present in both Branches.

#### **Course outcome (Course Skill Set)**

At the end of the course, the student will be able to:

- 1. Determine currents and voltages using source transformation/ source shifting/ mesh/ nodal analysis and reduce given network using star- delta transformation.

- 2. Solve problems by applying Network Theorems and electrical laws to reduce circuit complexities and to arrive at feasible solutions.

- 3. Analyse the circuit parameters during switching transients and apply Laplace transform to solve the given network

- 4. Evaluate the frequency response for resonant circuits and the network parameters for two port networks

#### **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

#### **Continuous Internal Evaluation:**

- There are 25 marks for the CIE's Assignment component and 25 for the Internal Assessment Test component.

- Each test shall be conducted for 25 marks. The first test will be administered after 40-50% of the coverage of the syllabus, and the second test will be administered after 85-90% of the coverage of the syllabus. The average of the two tests shall be scaled down to 25 marks

- Any two assignment methods mentioned in the 22OB2.4, if an assignment is project-based then only one assignment for the course shall be planned. The schedule for assignments shall be planned properly by the course teacher. The teacher should not conduct two assignments at the end of the semester if two assignments are planned. Each assignment shall be conducted for 25 marks. (If two assignments are conducted then the sum of the two assignments shall be scaled down to 25 marks)

- The final CIE marks of the course out of 50 will be the sum of the scale-down marks of tests and assignment/s marks.

Internal Assessment Test question paper is designed to attain the different levels of Bloom's taxonomy as per the outcome defined for the course.

#### **Semester-End Examination:**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (duration 03 hours).

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

- 3 The students have to answer 5 full questions selecting one full question from each module Suggested Learning Resources:

#### **Books**

- 1. M.E.Van Valkenburg (2000), Network Analysis, Prentice Hall of India, 3<sup>rd</sup>edition, 2000, ISBN:9780136110958.

- 2. Roy Choudhury-Networks and Systems, 2<sup>nd</sup> edition, New Age International Publications, 2006, ISBN: 9788122427677

# **ReferenceBooks:**

- 3. Hayt, Kemmerly and Durbin-Engineering Circuit Analysis, TMH7<sup>th</sup> Edition, 2010.

- 4. **J.**David Irwin/ R.Mark Nelms- Basic Engineering Circuit Analysis JohnWiley,8<sup>th</sup>ed,2006.

- 5. Charles K Alexander and Mathew NO Sadiku-Fundamentals of Electric Circuits, Tata McGraw-Hill,3rc1 Ed,2009.

| Web links and Video Lectures (e-Resources):                                          |

|--------------------------------------------------------------------------------------|

| • .                                                                                  |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

| Activity Based Learning (Suggested Activities in Class)/ Practical Based learning    |

| •                                                                                    |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

| Activity Based Learning (Suggested Activities in Class)/ Practical Based learning  • |

| Analog and Digital Syst        | tems Design Laboratory         | Semester       | 3   |

|--------------------------------|--------------------------------|----------------|-----|

| Course Code                    | BECL305                        | CIE Marks      | 50  |

| Teaching Hours/Week (L:T:P: S) | 0:0:2                          | SEE Marks      | 50  |

| Credits                        | 01                             | Exam Hours     | 100 |

| Examination type (SEE)         | Theory/Practical/Viva-Voce /Te | rm-work/Others |     |

This laboratory course enables students to

- Understand the electronic circuit schematic and its working

- Realize and test amplifier and oscillator circuits for the given specifications

- Realize the opamp circuits for the applications such as DAC, implement mathematical functions and precision rectifiers.

- Study the static characteristics of SCR and test the RC triggering circuit.

- Design and test the combinational and sequential logic circuits for their functionalities.

- Use the suitable ICs based on the specifications and functions.

| Sl.NO | Experiments (All the experiments has to be conducted using discrete components)                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Design and set up the BJT common emitter voltage amplifier with and without feedback and determine the gain- bandwidth product, input and output impedances.                                                                         |

| 2     | Design and set-up BJT/FET i) Colpitts Oscillator, ii) Crystal Oscillator                                                                                                                                                             |

| 3     | Design and set up the circuits using opamp: i) Adder, ii) Integrator, iii) Differentiator and iv) Comparator                                                                                                                         |

| 4     | Design 4-bit R – 2R Op-Amp Digital to Analog Converter (i) for a 4-bit binary input using toggle switches (ii) by generating digital inputs using mod-16                                                                             |

| 5     | Design and implement (a) Half Adder & Full Adder using basic gates and NAND gates, (b) Half subtractor & Full subtractor using NAND gates, (c) 4-variable function using IC74151(8:1MUX).                                            |

| 6     | Realize (i) Binary to Gray code conversion & vice-versa (IC74139), (ii) BCD to Excess-3 code conversion and vice versa                                                                                                               |

| 7     | a) Realize using NAND Gates: i) Master-Slave JK Flip-Flop, ii) D Flip-Flop and iii) T Flip-Flop b) Realize the shift registers using IC7474/7495: (i) SISO (ii) SIPO (iii) PISO (iv) PIPO (v) Ring counter and (vi) Johnson counter. |

| 8     | Realize a) Design Mod – N Synchronous Up Counter & Down Counter using 7476 JK Flip-flop b) Mod-N Counter using IC7490 / 7476 c) Synchronous counter using IC74192                                                                    |

|       | Demonstration Experiments ( For CIE )                                                                                                                                                                                                |

| 9     | Design and Test the second order Active Filters and plot the frequency response,  i) Low pass and Highpass Filter  ii) Bandpass and Bandstop Filter                                                                                  |

| 10    | Design and test the following using 555 timer  i) Monostable Multivibraator ii) Astable Multivibrator                                                                                                                                |

| 11    | Design and Test a Regulated Power supply                                                                                                                                                                                             |

| 12    | Design and test an audio amplifier by connecting a microphone input and observe the output using a loud speaker.                                                                                                                     |

#### Course outcomes (Course Skill Set):

At the end of the course the student will be able to:

- 1. Design and analyze the BJT/FET amplifier and oscillator circuits.

- 2. Design and test Opamp circuits to realize the mathematical computations, DAC and precision rectifiers.

- 3. Design and test the combinational logic circuits for the given specifications.

- 4. Test the sequential logic circuits for the given functionality.

- 5. Demonstrate the basic circuit experiments using 555 timer.

#### **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). A student shall be deemed to have satisfied the academic requirements and earned the credits allotted to each subject/ course if the student secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

#### **Continuous Internal Evaluation (CIE):**

CIE marks for the practical course are **50 Marks**.

The split-up of CIE marks for record/journal and test are in the ratio **60:40**.

- Each experiment is to be evaluated for conduction with an observation sheet and record write-up. Rubrics for the evaluation of the journal/write-up for hardware/software experiments are designed by the faculty who is handling the laboratory session and are made known to students at the beginning of the practical session.

- Record should contain all the specified experiments in the syllabus and each experiment write-up will be evaluated for 10 marks.

- Total marks scored by the students are scaled down to **30 marks** (60% of maximum marks).

- Weightage to be given for neatness and submission of record/write-up on time.

- Department shall conduct a test of 100 marks after the completion of all the experiments listed in the syllabus.

- In a test, test write-up, conduction of experiment, acceptable result, and procedural knowledge will carry a weightage of 60% and the rest 40% for viva-voce.

- The suitable rubrics can be designed to evaluate each student's performance and learning ability.

- The marks scored shall be scaled down to **20 marks** (40% of the maximum marks).

The Sum of scaled-down marks scored in the report write-up/journal and marks of a test is the total CIE marks scored by the student.

#### **Semester End Evaluation (SEE):**

- SEE marks for the practical course are 50 Marks.

- SEE shall be conducted jointly by the two examiners of the same institute, examiners are appointed by the Head of the Institute.

- The examination schedule and names of examiners are informed to the university before the conduction of the examination. These practical examinations are to be conducted between the schedule mentioned in the academic calendar of the University.

- All laboratory experiments are to be included for practical examination.

- (Rubrics) Breakup of marks and the instructions printed on the cover page of the answer script to be strictly adhered to by the examiners. **OR** based on the course requirement evaluation rubrics shall be decided jointly by examiners.

- Students can pick one question (experiment) from the questions lot prepared by the examiners jointly.

- Evaluation of test write-up/ conduction procedure and result/viva will be conducted jointly by examiners. General rubrics suggested for SEE are mentioned here, writeup-20%, Conduction procedure and result in -60%, Viva-voce 20% of maximum marks. SEE for practical shall be evaluated for 100 marks and scored marks shall

be scaled down to 50 marks (however, based on course type, rubrics shall be decided by the examiners)

Change of experiment is allowed only once and 15% of Marks allotted to the procedure part are to be made

The minimum duration of SEE is 02 hours

#### **Suggested Learning Resources:**

- 1. David A Bell, "Fundamentals of Electronic Devices and Circuits Lab Manual", 5th Edition, 2009, Oxford University Press.

- 2. Albert Malvino, David J Bates, Electronic Principles, 7th Edition, Mc Graw Hill Education, 2017.

- 3. Fundamentals of Logic Design, Charles H Roth Jr., Larry L Kinney, Cengage Learning, 7th Edition.

| Electi                         | ronic Devices | Semester    | 3   |

|--------------------------------|---------------|-------------|-----|

| Course Code                    | BEC306A       | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:0         | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40            | Total Marks | 100 |

| Credits                        | 03            | Exam Hours  | 3   |

| Examination type (SEE)         | Theory        |             |     |

#### **Course objectives:** This course will enable students to:

- Understand the basics of semiconductor physics and electronic devices.

- Describe the mathematical models BJTs and FETs along with the constructional details.

- Understand the construction and working principles of optoelectronic devices

- Understand the fabrication process of semiconductor devices and CMOS process integration.

#### **Teaching-Learning Process (General Instructions)**

These are sample Strategies, which teachers can use to accelerate the attainment of the various course outcomes.

These are sample Strategies, which teacher can use to accelerate the attainment of the various course outcomes.

- Lecture method(L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- Encourage collaborative(Group)Learning in the class.

- Ask at least three HOTS(Higher order Thinking) questions in the class, which promotes critical thinking.

- Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyze information rather than simply recall it.

- Topics will be introduced in a multiple representation.

- Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

- Discuss how every concept can be applied to the realworld-and when that's possible, it helps improve the students' understanding.

- Adopt Flipped class technique by sharing the materials/Sample Videos prior to the class and have discussions on the topic in the succeeding classes.

#### Module-1

#### Semiconductors

Bonding forces in solids, Energy bands, Metals, Semiconductors and Insulators, Direct and Indirect semiconductors, Electrons and Holes, Intrinsic and Extrinsic materials, Conductivity and Mobility, Drift and Resistance, Effects of temperature and doping on mobility, Hall Effect.

(Text1: 3.1.1, 3.1.2, 3.1.3, 3.1.4, 3.2.1, 3.2.3, 3.2.4, 3.4.1, 3.4.2, 3.4.3, 3.4.5).

#### Module-2

#### **PN Junctions**

Forward and Reverse biased junctions-Qualitative description of Current flow at a junction, reverse bias, Reverse bias breakdown- Zener breakdown, avalanche breakdown, Rectifiers.(**Text1:5.3.1,5.3.3,5.4,5.4.1,5.4.2,5.4.3**) Optoelectronic Devices Photodiodes: Current and Voltage in an Illuminated Junction, Solar Cells, Photodetectors. Light Emitting Diode: Light Emitting materials.

(Text1:8.1.1,8.1.2,8.1.3,8.2,8.2.1),

#### Module-3

#### **Bipolar Junction Transistor**

Fundamentals of BJT operation, Amplification with BJTS,BJT Fabrication, The coupled Diode model(Ebers-Moll Model),Switching operation of a transistor, Cutoff, saturation, switching cycle, specifications, Drift in the base region, Base narrowing, Avalanche breakdown.

(Text1:7.1,7.2,7.3,7.5.1,7.6,7.7.1,7.7.2, 7.7.3)

#### Module-4

#### **Field Effect Transistors**

Basic pn JFET Operation, Equivalent Circuit and Frequency Limitations, MOSFET-Two terminal MO Sstructure-Energy band diagram, Ideal Capacitance

-Voltage Characteristics and Frequency Effects, Basic MOSFET Operation- MOSFET structure, Current-Voltage Characteristics.

(Text2:9.1.1,9.4,9.6.1,9.6.2,9.7.1,9.7.2,9.8.1,9.8.2).

#### Module-5

#### **Fabrication of p-n junctions**

Thermal Oxidation, Diffusion, Rapid Thermal Processing, Ion implantation, chemical vapour deposition, photolithography, Etching, metallization. (**Text 1: 5.1**)

#### **Integrated Circuits**

Background, Evolution of ICs, CMOS Process Integration, Integration of Other Circuit Elements.(**Text 1:9.1,9.2,9.3.1,9.3.3**).

#### Course outcome (Course Skill Set)

At the end of the course, the student will be able to:

- 1. Understand the principles of semiconductor Physics

- 2. Understand the principles and characteristics of different types of semiconductor devices

- 3. Understand the fabrication process of semiconductor devices

- 4. Utilize the mathematical models of semiconductor junctions for circuits and systems.

- 5. Identify the mathematical models of MOS transistors for circuits and systems.

#### **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

#### **Continuous Internal Evaluation:**

- There are 25 marks for the CIE's Assignment component and 25 for the Internal Assessment Test component.

- Each test shall be conducted for 25 marks. The first test will be administered after 40-50% of the coverage of the syllabus, and the second test will be administered after 85-90% of the coverage of the syllabus. The average of the two tests shall be scaled down to 25 marks

- Any two assignment methods mentioned in the 220B2.4, if an assignment is project-based then

only one assignment for the course shall be planned. The schedule for assignments shall be

planned properly by the course teacher. The teacher should not conduct two assignments at the

end of the semester if two assignments are planned. Each assignment shall be conducted for 25

marks. (If two assignments are conducted then the sum of the two assignments shall be scaled

down to 25 marks)

- The final CIE marks of the course out of 50 will be the sum of the scale-down marks of tests and assignment/s marks.

Internal Assessment Test question paper is designed to attain the different levels of Bloom's taxonomy as per the outcome defined for the course.

#### **Semester-End Examination:**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (duration 03 hours).

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

- 3. The students have to answer 5 full questions, selecting one full question from each module.

- 4. Marks scored shall be proportionally reduced to 50 marks

#### **Suggested Learning Resources:**

#### Books

- 1. Ben. G. Streetman, Sanjay Kumar Banerjee, "Solid State Electronic Devices",7<sup>th</sup>Edition,Pearson Education,2016,ISBN978-93-325-5508-2.

- 2. Donald A Neamen, Dhrubes Biswas, "Semiconductor Physics and Devices", 4th Edition, McGraw Hill Education, 2012, ISBN 978-0-07-107010-2.

#### ReferenceBooks:

- 3. S.M.Sze, Kwok K.Ng, "Physics of Semiconductor Devices", 3<sup>rd</sup> Edition, Wiley, 2018.

- 4. AdirBar-Lev,"SemiconductorandElectronicDevices",3<sup>rd</sup>Edition,PHI, 1993

### Web links and Video Lectures (e-Resources):

| • .                                                                                  |  |

|--------------------------------------------------------------------------------------|--|

|                                                                                      |  |

|                                                                                      |  |

|                                                                                      |  |

| Activity Based Learning (Suggested Activities in Class)/ Practical Based learning    |  |

| Activity Based Learning (Suggested Activities in Class)/ Practical Based learning  • |  |

| • Class)/ Practical Based learning •                                                 |  |

| Sensors and In                 | strumentation | Semester    | 3   |

|--------------------------------|---------------|-------------|-----|

| Course Code                    | BEC306B       | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:0         | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40            | Total Marks | 100 |

| Credits                        | 03            | Exam Hours  | 3   |

| Examination type (SEE)         | Theory        |             |     |

- Understand various technologies associated in manufacturing of sensors

- Acquire knowledge about types of sensors used in modern digital systems

- Get acquainted about material properties required to make sensors

- Understand types of instrument errors and circuits for multirange Ammeters and Voltmeters.

- Describe principle of operation of digital measuring instruments and Bridges.

- Understand the operations of transducers and instrumentation amplifiers.

# **Teaching-Learning Process (General Instructions)**

These are sample Strategies, which teacher can use to accelerate the attainment of the various course outcomes.

- Lecture method(L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- Encourage collaborative(Group)Learning in the class.

- Ask at least three HOTS(Higher order Thinking)questions in the class, which promotes critical thinking.

- Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyze information rather than simply recall it.

- Topics will be introduced in a multiple representation.

- Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

- Discuss how every concept can be applied to the realworld-and when that's possible, it helps improve the students' understanding.

- Adopt Flipped class technique by sharing the materials/Sample Videos prior to the class and have discussions on the topic in the succeeding classes.

#### Module-1

#### **Introduction to sensor based measurement systems:**

General concepts and terminology, sensor classification, Primary Sensors, material for sensors, microsensor technology. (Text 1)

#### **Module-2**

**Self-generating** Sensors-Thermoelectric sensors, piezoelectric sensors, pyroelectric sensors, photovoltaic sensors, electrochemical sensors. (Text 1)

#### Module-3

**Principles of Measurement:** Static Characteristics, Error in Measurement, Types of Static Error.(Text 2: 1.2-1.6)

Multirange Ammeters, Multirange voltmeter.(Text2:3.2,4.4)

**Digital Voltmeter:** Ramp Technique, Dual slope integrating Type DVM, Direct Compensation type and Successive Approximations type DVM (Text 2: 5.1-5.3, 5.5,5.6)

#### **Module-4**

**Digital Multimeter:** Digital Frequency Meter and Digital Measurement of Time, Function Generator. **Bridges:** Measurement of resistance: Wheatstone's Bridge, AC Bridges - Capacitance and Inductance Comparison bridge, Wien's bridge.

(Text2:refer 6.2,6.3 up to 6.3.2, 6.4 up to 6.4.2, 8.8, 11.2, 11.8 -11.10, 11.14).

#### **Module-5**

**Transducers:** Introduction, Electrical Transducer, Resistive Transducer, Resistive position Transducer, Resistance Wire Strain Gauges, Resistance Thermometer, Thermistor, LVDT.

(Text2:13.1-13.3,13.5, 13.6 up to 13.6.1,13.7,13.8,13.11).

Instrumentation Amplifier using Transducer Bridge, Temperature indicators using Thermometer, Analog Weight Scale(Text2:14.3.3, 14.4.1, 14.4.3).

### **Course outcome (Course Skill Set)**

At the end of the course, the student will be able to:

- 1. Understand the material properties required to make sensors

- 2. Understand the principle of transducers for measuring physical parameters.

- 3. Describe the manufacturing process of sensors

- 4. Analyze the instrument characteristics and errors.

- 5. Describe the principle of operation and develop circuits for multirange Ammeters, Voltmeters and Bridges to measure passive component values and frequency.

#### **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

#### **Continuous Internal Evaluation:**

- There are 25 marks for the CIE's Assignment component and 25 for the Internal Assessment Test component.

- Each test shall be conducted for 25 marks. The first test will be administered after 40-50% of the coverage of the syllabus, and the second test will be administered after 85-90% of the coverage of the syllabus. The average of the two tests shall be scaled down to 25 marks

- Any two assignment methods mentioned in the 22OB2.4, if an assignment is project-based then only one assignment for the course shall be planned. The schedule for assignments shall be planned properly by the course teacher. The teacher should not conduct two assignments at the end of the semester if two assignments are planned. Each assignment shall be conducted for 25 marks. (If two assignments are conducted then the sum of the two assignments shall be scaled down to 25 marks)

- The final CIE marks of the course out of 50 will be the sum of the scale-down marks of tests and assignment/s marks.

Internal Assessment Test question paper is designed to attain the different levels of Bloom's taxonomy as per the outcome defined for the course.

#### **Semester-End Examination:**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (duration 03 hours).

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions), **should have a mix of topics** under that module.

- 3. The students have to answer 5 full questions, selecting one full question from each module.

- 4. Marks scored shall be proportionally reduced to 50 marks

# **Suggested Learning Resources:**

#### **Books**

- 1. "Sensors and Signal Conditioning", Ramon Pallas Areny, JohnG. Webster,2<sup>nd</sup> edition, John Wiley and Sons,2000

- 2. H.S.Kalsi, "Electronic Instrumentation", Mc Graw Hill, 3<sup>rd</sup> Edition, 2012, ISBN: 9780070702066.

#### Reference Books

- 1. DavidA. Bell,"Electronic Instrumentation & Measurements", Oxford University Press PHI 2<sup>nd</sup>Edition, 2006,ISBN 81-203-2360-2.

- **2.** D. HelfrickandW.D. Cooper, "Modern Electronic Instrumentation and Measuring Techniques", Pearson, 1<sup>st</sup>Edition, 2015, ISBN: 9789332556065.

#### Web links and Video Lectures (e-Resources):

| • .                                                                               |  |

|-----------------------------------------------------------------------------------|--|

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

| Activity Based Learning (Suggested Activities in Class)/ Practical Based learning |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

|                                                                                   |  |

| Computer Organization          | n and Architecture | Semester    | 3   |

|--------------------------------|--------------------|-------------|-----|

| Course Code                    | BEC306C            | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:0              | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40                 | Total Marks | 100 |

| Credits                        | 03                 | Exam Hours  | 3   |

| Examination type (SEE)         | Theory             |             |     |

**Course objectives:** This course will enable students to:

- Explain the basic sub systems of a computer, their organization, structure and operation.

- Illustrate the concept of programs as sequences of machine instructions.

- Demonstrate different ways of communicating with I/O devices

- Describe memory hierarchy and concept of virtual memory.

- Illustrate organization of simple pipelined processor and other computing systems.

# **Teaching-Learning Process (General Instructions)**

These are sample Strategies, which teachers can use to accelerate the attainment of the various course outcomes.

These are sample Strategies, which teacher can use to accelerate the attainment of the various course outcomes.

- Lecture method (L) does not mean only traditional lecture method, but different type of teaching methods may be adopted to develop the outcomes.

- Encourage collaborative (Group) Learning in the class.

- Ask at least three HOTS(Higher order Thinking)questions in the class, which promotes critical thinking.

- Adopt Problem Based Learning (PBL), which fosters students' Analytical skills, develop thinking skills such as the ability to evaluate, generalize, and analyze information rather than simply recall it.

- Topics will be introduced in a multiple representation.

- Show the different ways to solve the same problem and encourage the students to come up with their own creative ways to solve them.

- Discuss how every concept can be applied to the real world-and when that's possible, it helps improve the students' understanding.

- Adopt Flipped class technique by sharing the materials/Sample Videos prior to the class and have discussions on the topic in the succeeding classes.

#### Module-1

**Basic Structure of Computers:** Computer Types, Functional Units, Basic Operational Concepts, Bus Structures, Software, Performance -Processor Clock, Basic Performance Equation(upto1.6.2ofChap1ofText).

Machine Instructions and Programs: Numbers, Arithmetic Operations and Characters, IEEE standard for Floating point Numbers, Memory Location and Addresses, Memory Operations, Instructions and Instruction Sequencing (up to 2.4.6 of Chap 2 and 6.7.1 of Chap 6 of Text).

#### Module-2

Addressing Modes, Assembly Language, Basic Input and Output Operations, Stacks and Queues, Subroutines, Additional Instructions (from 2.4.7 of Chap 2, except 2.9.3, 2.11 & 2.12 of Text).

#### **Module-3**

**Input/ Output Organization:** Accessing I/O Devices, Interrupts -Interrupt Hardware, Enabling and Disabling Interrupts, Handling Multiple Devices, Controlling Device Requests, Direct Memory Access (upto4.2.4and4.4except4.4.1ofChap4ofText).

#### **Module-4**

**Memory System:** Basic Concepts, Semiconductor RAM Memories-Internal organization of memory chips, Static memories, Asynchronous DRAMS, Read Only Memories, Cash Memories, Virtual Memories, Secondary Storage- Magnetic Hard Disks (5.1,5.2,5.2.1,5.2.2,5.2.3,5.3,5.5(except 5.5.1 to 5.5.4), 5.7 (except5.7.1), 5.9, 5.9.1 of Chap 5 of Text).

#### **Module-5**

Basic Processing Unit: Some Fundamental Concepts, Execution of a Complete Instruction, Multiple Bus Organization, Hardwired Control, Microprogrammed Control (up to 7.5 except 7.5.1 to 7.5.6 of Chap 7 of Text).

# **Course outcome (Course Skill Set)**

At the end of the course, the student will be able to:

- 1. Explain the basic organization of a computer system.

- 2. Describe the addressing modes, instruction formats and program control statement.

- 3. Explain different ways of accessing an input/ output device including interrupts.

- 4. Illustrate the organization of different types of semiconductor and other secondary storage memories.

- 5. Illustrate simple processor organization based on hard wired control and microprogrammed control.

# **Assessment Details (both CIE and SEE)**

The weightage of Continuous Internal Evaluation (CIE) is 50% and for Semester End Exam (SEE) is 50%. The minimum passing mark for the CIE is 40% of the maximum marks (20 marks out of 50) and for the SEE minimum passing mark is 35% of the maximum marks (18 out of 50 marks). The student is declared as a pass in the course if he/she secures a minimum of 40% (40 marks out of 100) in the sum total of the CIE (Continuous Internal Evaluation) and SEE (Semester End Examination) taken together.

#### **Continuous Internal Evaluation:**

- There are 25 marks for the CIE's Assignment component and 25 for the Internal Assessment Test component.

- Each test shall be conducted for 25 marks. The first test will be administered after 40-50% of the coverage of the syllabus, and the second test will be administered after 85-90% of the coverage of the syllabus. The average of the two tests shall be scaled down to 25 marks

- Any two assignment methods mentioned in the 22OB2.4, if an assignment is project-based then only one assignment for the course shall be planned. The schedule for assignments shall be planned properly by the course teacher. The teacher should not conduct two assignments at the end of the semester if two assignments are planned. Each assignment shall be conducted for 25 marks. (If two assignments are conducted then the sum of the two assignments shall be scaled down to 25 marks)

- The final CIE marks of the course out of 50 will be the sum of the scale-down marks of tests and assignment/s marks.

Internal Assessment Test question paper is designed to attain the different levels of Bloom's taxonomy as per the outcome defined for the course.

#### **Semester-End Examination:**

Theory SEE will be conducted by University as per the scheduled timetable, with common question papers for the course (duration 03 hours).

- 1. The question paper will have ten questions. Each question is set for 20 marks.

- 2. There will be 2 questions from each module. Each of the two questions under a module (with a maximum of 3 sub-questions) should have a mix of tonics under that module

# **Suggested Learning Resources:**

#### Book

1. Carl Hamacher, Zvonko Vranesic, Safwat Zaky: Computer Organization, 5<sup>th</sup>Edition,Tata McGrawHill,2002.

#### **ReferenceBooks:**

- 2. David A. Patterson, John L. Hennessy: Computer Organization and Design-The Hardware/Software InterfaceARM Edition, 4<sup>th</sup> Edition, Elsevier, 2009.

- 3. William Stallings: Computer Organization & Architecture, 7<sup>th</sup> Edition, PHI, 2006.

- 4. Vincent P. Heuring & Harry F. Jordan: Computer Systems Design and Architecture, 2<sup>nd</sup> Edition, Pearson Education, 2004.

| Web links and Video Lectures (e-Resources):                                       |

|-----------------------------------------------------------------------------------|

| • .                                                                               |

|                                                                                   |

|                                                                                   |

|                                                                                   |

| Activity Based Learning (Suggested Activities in Class)/ Practical Based learning |

| •                                                                                 |

|                                                                                   |

|                                                                                   |

| Applied Numerical Me           | ethods for EC Engineers | Semester    | 3   |

|--------------------------------|-------------------------|-------------|-----|

| Course Code                    | BEC306D                 | CIE Marks   | 50  |

| Teaching Hours/Week (L:T:P: S) | 3:0:0:0                 | SEE Marks   | 50  |

| Total Hours of Pedagogy        | 40                      | Total Marks | 100 |

| Credits                        | 03                      | Exam Hours  | 03  |

| Examination type (SEE)         | Theory                  |             |     |

- To provide the knowledge and importance of error analysis in engineering problems

- To represent and solve an application problem using a system of linear equations